1      Supplementary Information: A 3D-integrated

2      BiCMOS-silicon photonics high-speed receiver

3      realized using micro-transfer printing

Ye Gu<sup>1\*†</sup>, He Li<sup>2\*†</sup>, Tinus Pannier<sup>1†</sup>, Shengpu Niu<sup>1</sup>,

Patrick Heise<sup>3,4</sup>, Christian Mai<sup>3</sup>, Prasanna Ramaswamy<sup>5</sup>,

Alex Farrell<sup>5</sup>, Alin Fecioru<sup>5</sup>, Antonio Jose Trindade<sup>5</sup>,

Ruggero Loi<sup>5</sup>, Nishant Singh<sup>1</sup>, Senbiao Qin<sup>2</sup>, Biwei Pan<sup>2</sup>,

Jing Zhang<sup>2</sup>, Johanna Rimböck<sup>6</sup>, Kristof Dhaenens<sup>7</sup>,

Toon De Baere<sup>7</sup>, Geert Van Steenberge<sup>7</sup>, Dieter Bode<sup>8</sup>,

Dimitrios Velenis<sup>8</sup>, Guy Lepage<sup>8</sup>, Neha Singh<sup>8</sup>,

Joris Van Campenhout<sup>8</sup>, Xin Yin<sup>1</sup>, Günther Roelkens<sup>2\*</sup>,

Peter Ossieur<sup>1\*</sup>

<sup>13</sup> <sup>1</sup>IDLab, INTEC, Ghent University – imec, Ghent, 9052, Belgium.

14 <sup>2</sup>Photonics Research Group, INTEC, Ghent University – imec, Ghent,

15 9052, Belgium.

<sup>3</sup>IHP- Leibniz-Institut für innovative Mikroelektronik, Frankfurt (Oder), Germany.

<sup>5</sup> X-Celeprint Ltd., Lee Maltings, Dyke Parade, Cork, Ireland.

<sup>6</sup> EV Group, E. Thallner GmbH, St. Florian am Inn, Austria.

22 <sup>7</sup>Center for Microsystems Technology (CMST), INTEC, imec – Ghent

23 University, Ghent, 9052, Belgium.

<sup>8</sup>imec, Kapeldreef 75, Leuven, 3001, Belgium.

\*Corresponding author(s). E-mail(s): [Ye.Gu@ugent.be](mailto:Ye.Gu@ugent.be); [He.Li@ugent.be](mailto:He.Li@ugent.be);

Gunther.Roelkens@ugent.be; Peter.Ossieur@imec.be;

Contributing authors: [Tinus.Pannier@ugent.be](mailto:Tinus.Pannier@ugent.be);

<sup>†</sup>These authors contributed equally to this work.

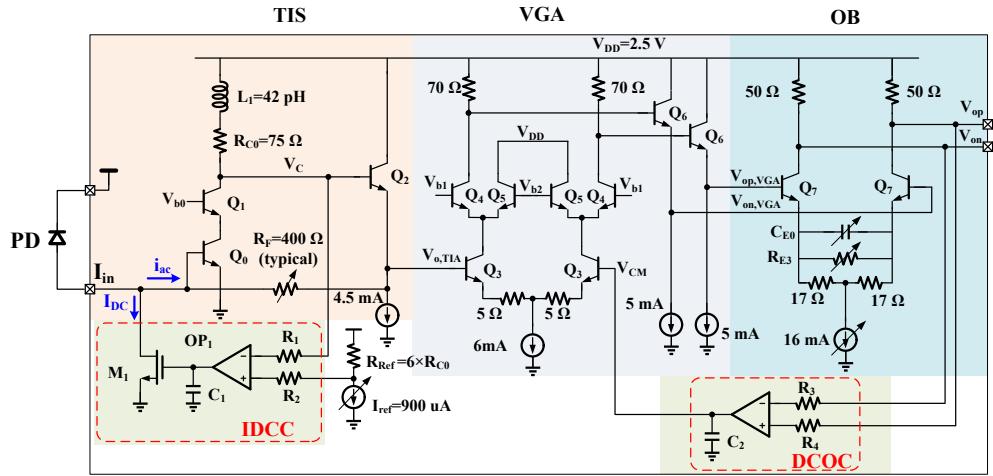

## 29 1 Transimpedance amplifier chiplet

30 The simplified schematic of the transimpedance amplifier (TIA) chiplet is shown in

31 Fig. 1. The TIA input stage (TIS) utilizes a typical shunt feedback structure to convert

32 the AC current signal of the PD into a voltage signal. Two electrostatic discharge

33 (ESD) diodes, with a total of 51 fF parasitic capacitance, are placed at the input

34 of the TIS to protect the internal circuits.  $Q_1$  serves to alleviate the Miller effect of

35 the parasitic base-collector capacitor of  $Q_0$ . A shunt inductor  $L_1$ , with  $25 \times 25 \mu\text{m}^2$

36 area, is used to increase the phase margin of the TIA loop. The feedback resistor  $R_F$ ,

37 implemented as NMOS transistors and a polysilicon resistor, can be adapted by digital

38 bits to compensate for the process variation.  $M_1$  in the input DC current cancellation

39 (IDCC) is used to absorb the DC current of the PD and the DC current of  $R_F$ .  $C_1$  is

40 used to compensate for the IDCC loop and alleviate the baseline wander.  $R1 = 4k\Omega$ ,

41 placed close to the base of  $Q_2$ , is used to prevent the parasitic capacitance of the

42 IDCC from affecting the high-speed path. As  $R_{Ref} = 6 \times R_{C0}$ , the  $Q_0$  collector current

43  $I_{C,Q_0} \approx 6 \times I_{ref} = 5.4\text{mA}$ , which impacts the overall bandwidth and input-referred

44 noise current of the TIA.  $I_{ref}$  is designed to be tunable and controlled by digital

45 registers.  $R_{Ref}$  and  $R_{C0}$  are placed close to each other in the layout for matching.

Fig. 1 Simplified schematic of the TIA chiplet.

46 The DC voltage at the input of the TIS is equal to one base-emitter forward bias

47 voltage  $V_{be,Q_0} \approx 0.75\text{V}$ . The PD cathode bias voltage can be chosen to be the same

48 as the main supply voltage of 2.5 V, so that the PD is reversely biased with a  $\sim 1.75$

49 V voltage difference.

50 The TIS is followed by the variable gain amplifier (VGA) stage, which also serves

51 as a single-to-differential converter. One input of the VGA is connected to the output

52 of the TIS, the other input is connected to a reference voltage generated by the DCOC.

53 The gain of the VGA can be fine-tuned by changing  $V_{b1}$  and  $V_{b2}$  through digital bits.

54 Two  $50\ \Omega$  resistors are used for impedance matching in the output buffer (OB)

55 stage. The OB stage has a tunable CTLE, realized by a tunable capacitor  $C_{E0}$  and a

56 tunable resistor  $R_{E3}$ . The  $R_{E3}$  is realized using NMOS transistors in the triode region,

57 whose resistance is programmable by tuning their gate voltages. The  $C_{E0}$  is realized

58 using PMOS varicaps, which can be fine-tuned by digital registers. The differential

59 outputs of the OB are also protected by ESD diodes.

## 60 2 Comparison with current state-of-the-art optical 61 receivers using different integrations

62 Table 1 shows the comparison with the state-of-the-art IMDD optical receivers using

63 different integration methods. This  $\mu$ TP based optical receiver achieves the lowest

64 power consumption of 0.51 pJ/b and the smallest EIC area of 0.06  $mm^2$ .

**Table 1** Comparison with current state-of-the-art PAM-4 optical receivers using different integrations.

| ref.      | Integration         | EIC technology | Data rate (Gb/s) | $R_T$ (dBΩ) | R (A/W) | Sens. @KP4 (dBm) | pJ/b | EIC Area ( $mm^2$ ) | DSP                    |

|-----------|---------------------|----------------|------------------|-------------|---------|------------------|------|---------------------|------------------------|

| [1]       | Wire-bonding (2D)   | 130nm BiCMOS   | 160              | 65          | 0.8     | -7               | 0.99 | 0.82 <sup>1</sup>   | 5-tap FFE              |

| [2]       | Wire-bonding (2D)   | 55nm BiCMOS    | 224              | 57.3        | 0.89    | -4.8             | 2.2  | 1.38 <sup>1</sup>   | 10-tap FFE             |

| [3]       | Flip-chip (3D)      | N/A            | 160              | N/A         | 0.85    | -2.7             | 1.2  | N/A                 | 51-tap FFE             |

| [4]       | Flip-chip (3D)      | 16nm FinFET    | 106.25           | 77          | N/A     | -13.97           | 0.98 | 0.64                | 12-tap FFE + 1-tap DFE |

| [5]       | Direct-bonding (3D) | 130nm BiCMOS   | 264              | 60          | 0.9     | N/A              | 1.45 | 0.6                 | 6-tap FFE              |

| [6]       | Monolithic          | 45nm CMOS      | 112              | 68          | 0.245   | N/A              | 1    | N/A                 | N/A                    |

| This work | $\mu$ TP (3D)       | 130nm BiCMOS   | 224              | 53.6        | 0.9     | -5.2             | 0.51 | 0.06                | 6-tap FFE              |

<sup>1</sup> data path core of one channel.

## 65 References

66 [1] Gu, Y., Lambrecht, J., Niu, S., Vandierendonck, A., Bruynsteen, C., Coudyzer,

67 G., De Bruyn, K., Bauwelinck, J., Yin, X., Ossieur, P.: A 160 Gb/s PAM-4 opti-

68 cal receiver using a fully differential transimpedance amplifier in SiGe BiCMOS.

69 Journal of Lightwave Technology **42**(23), 8237–8244 (2024)

70 [2] Declercq, J., Moeneclaey, B., Lambrecht, J., Bruynsteen, C., Singh, N., Niu, S.,

71 Ossieur, P., Yin, X.: A 64-GHz optical receiver for 128-GBd links using a 55-

72 nm SiGe BiCMOS traveling-wave linear transimpedance amplifier. Journal of

73 Lightwave Technology, 1–10 (2025)

74 [3] Wu, D., Wang, D., Chen, D., Yan, J., Dang, Z., Feng, J., Chen, S., Feng, P., Zhang,

75 H., Fu, Y., *et al.*: Experimental demonstration of a 160 Gbit/s 3D-integrated sili-

76 con photonics receiver with 1.2-pJ/bit power consumption. Optics Express **31**(3),

77 4129–4139 (2023)

78 [4] Lakshmikumar, K., Kurylak, A., Nandwana, R.K., Das, B., Pampanin, J.,

79 Brubaker, M., Hanumolu, P.K.: A 7 pA/ $\sqrt{\text{Hz}}$  asymmetric differential TIA for

80 100Gb/s PAM-4 links with -14dBm optical sensitivity in 16nm CMOS. In: 2023

81 IEEE International Solid-State Circuits Conference (ISSCC), pp. 206–208 (2023)

82 [5] Peczek, A., Wietstruck, M., Winzer, G., Mai, C., Lischke, S., Khafaji, M.M.,

83 Schulze, S., Voß, T., Krüger, P., Zimmermann, L.: 132 GBaud PAM4 IM/DD sil-

84 icon receiver subassembly realized by stacking technology. Journal of Lightwave

85 Technology, 1–6 (2025)

86 [6] Baehr-Jones, T., Ardalan, S., Chang, M., Jafarlou, S., Serey, X., Zarris, G., Thomp-

87 son, G., Darbinian, A., West, B., Behnia, B., Velev, V., Li, Y.Z., Roelofs, K., Wu,

88 W., Mali, J., Zhan, J., Ophir, N., Horng, C., Narevich, R., Guan, F., Yang, J.,

89 Wu, H., Maupin, P., Manley, R., Ahuja, Y., Novack, A., Wang, L., Streshinsky,

90 M.: Monolithically integrated 112 gbps pam4 optical transmitter and receiver in a

91 45nm cmos-silicon photonics process. Optics Express **31**(15), 24926–24938 (2023)