1                   **A fully-memristive trimodal fusion perception system integrating**

2                   **multisensory neuron with hybrid neural network accelerator**

3                   Mingyang Wang<sup>1</sup>, Ruiqing Xie<sup>2</sup>, Linbo Shan<sup>2</sup>, Dong Wang<sup>1</sup>, Fan Yue<sup>1</sup>, Xinyi He<sup>1</sup>, Kai Liu<sup>1</sup>, Ruizhe Zhang<sup>1</sup>,

4                   Xiaodong Huang<sup>1\*</sup>, Zongwei Wang<sup>2\*</sup>, Chuanyu Han<sup>3\*</sup>, Lindong Wu<sup>1\*</sup>, Yimao Cai<sup>2</sup>

5                   <sup>1</sup>School of Integrated Circuits, Southeast University, Nanjing, China. <sup>2</sup>School of Integrated Circuits, Beijing Advanced

6                   Innovation Center for Integrated Circuits, Peking University, Beijing, China. <sup>3</sup>School of Microelectronics, Xi'an

7                   Jiaotong University, Xi'an, China.

8                   Email: xdhuang@seu.edu.cn, wangzongwei@pku.edu.cn, hanchuanyu@xjtu.edu.cn, wulindong@seu.edu.cn

9                   This supplementary information includes:

10                  Supplementary Note 1 to 8

11                  Supplementary Figure 1 to 24

12                  Supplementary Table 1 to 5

13                  Supplementary References

14

15 **a** Memristive sensory neuron:

16 Limited information fusion capability

17 **b** Reconfigurable CMOS neuron:

18 Large area and high circuit complexity

14

15 **Supplementary Figure 1. a**, Schematic of a memristive sensory neuron with limited information fusion capability. Existing

16 memristive sensory neurons are generally limited to fusing no more than two modalities. **b**, Schematic of a reconfigurable CMOS

17 neuron with large area and high circuit complexity. Existing reconfigurable CMOS neurons typically rely on complex control logic

18 and operate in a time-multiplexed manner.

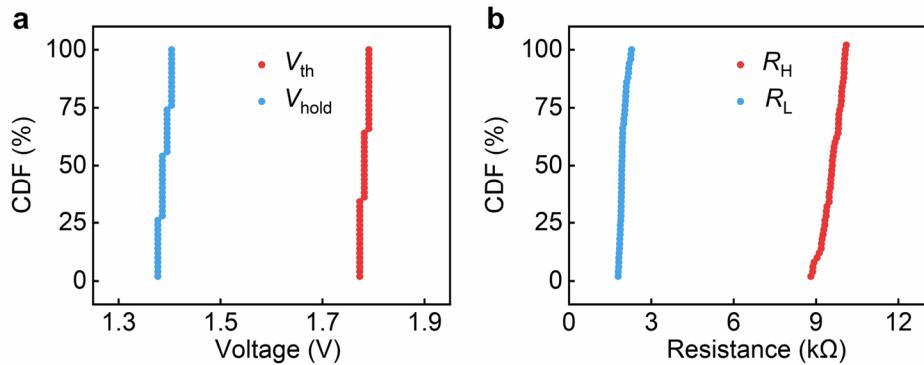

19 **Supplementary Note 1. Performance of the NbO<sub>x</sub> memristor.**

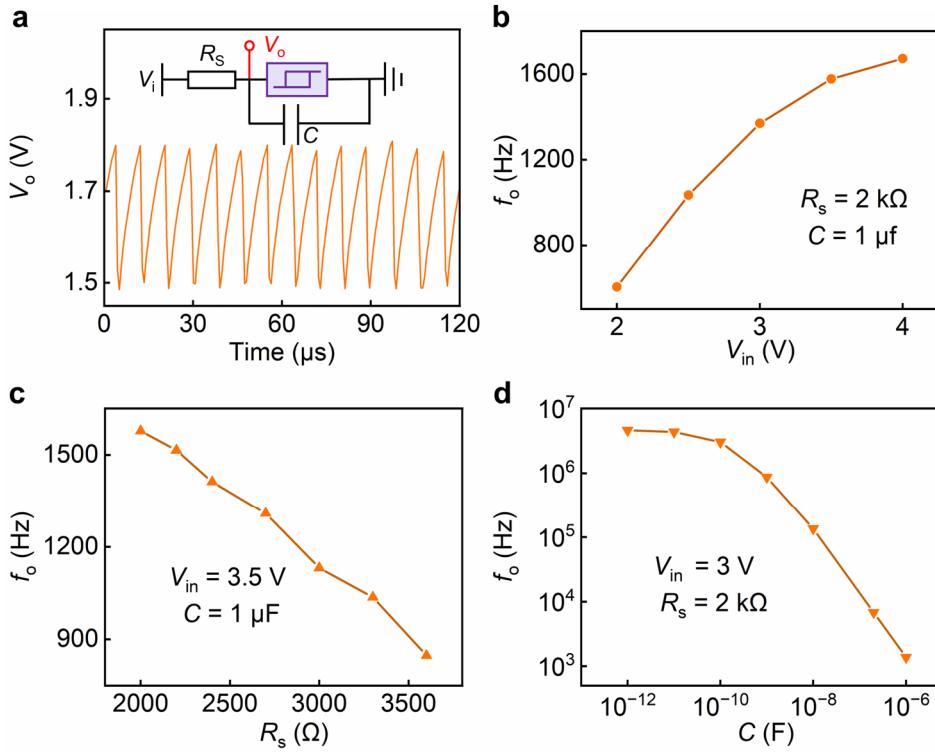

20 Supplementary Fig. 2a-b present the cumulative plots of  $V_{\text{th}}$ ,  $V_{\text{hold}}$ ,  $R_{\text{H}}$  and  $R_{\text{L}}$  across 50 cycles. Using the NbO<sub>x</sub>

21 memristor, together with resistors and capacitors, the oscillation circuit shown in Supplementary Fig. 3a can be further

22 constructed. In this configuration, the NbO<sub>x</sub> memristor is connected in parallel with a capacitor ( $C$ ), and this parallel

23 branch is then connected in series with a load resistor ( $R_{\text{S}}$ ). When a voltage stimulus ( $V_{\text{i}}$ ) is applied, the capacitor in the

24 oscillation circuit enters a charging phase and the output voltage ( $V_{\text{o}}$ ) increases. Once the  $V_{\text{o}}$  exceeds  $V_{\text{th}}$ , the device

25 switches to the LRS, initiating the discharging phase and causing  $V_{\text{o}}$  to drop. As  $V_{\text{o}}$  falls below  $V_{\text{hold}}$ , the device reverts

26 to the HRS, and the capacitor begins charging again, resulting in a rise in  $V_{\text{o}}$ . This process produces periodic output

27 spikes. Moreover, the oscillation frequency ( $f_{\text{o}}$ ) depends on the series resistance, the parallel capacitance and the

28 magnitude of the input voltage. Supplementary Fig. 3b-c illustrate the relationships between  $f_{\text{o}}$  and  $V_{\text{i}}$ ,  $R_{\text{S}}$  and  $C$ .

29 **Supplementary Figure 2. a**, Distribution of the extracted  $V_{\text{th}}$  and  $V_{\text{hold}}$  from 50 I-V sweeps. **b**, Distribution of the extracted  $R_{\text{H}}$  and

30  $R_{\text{L}}$  from 50 I-V sweeps.

31 **Supplementary Figure 3.** **a**, Circuit structure and output oscillation signal of the  $\text{NbO}_x$ -based oscillator. **b-d**, Effects of  $V_{in}$  (c),  $R_s$  (d) and  $C$  (e) on  $f_o$ .

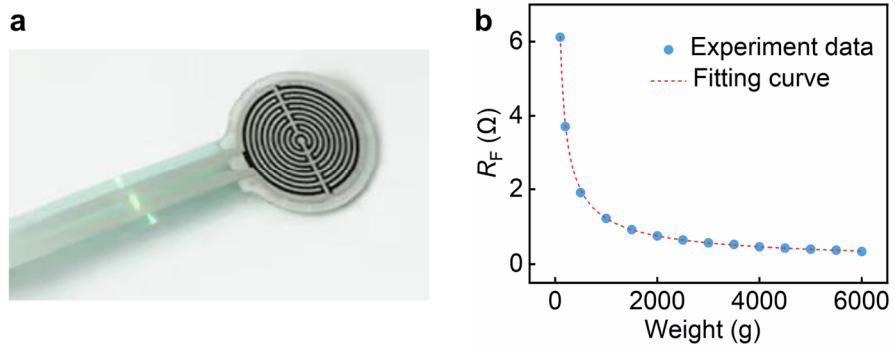

33 **Supplementary Figure 4. a**, Photograph of the piezoresistive sensor used in the circuit. **b**, Resistance-pressure response curve of

34 the piezoresistive sensor.

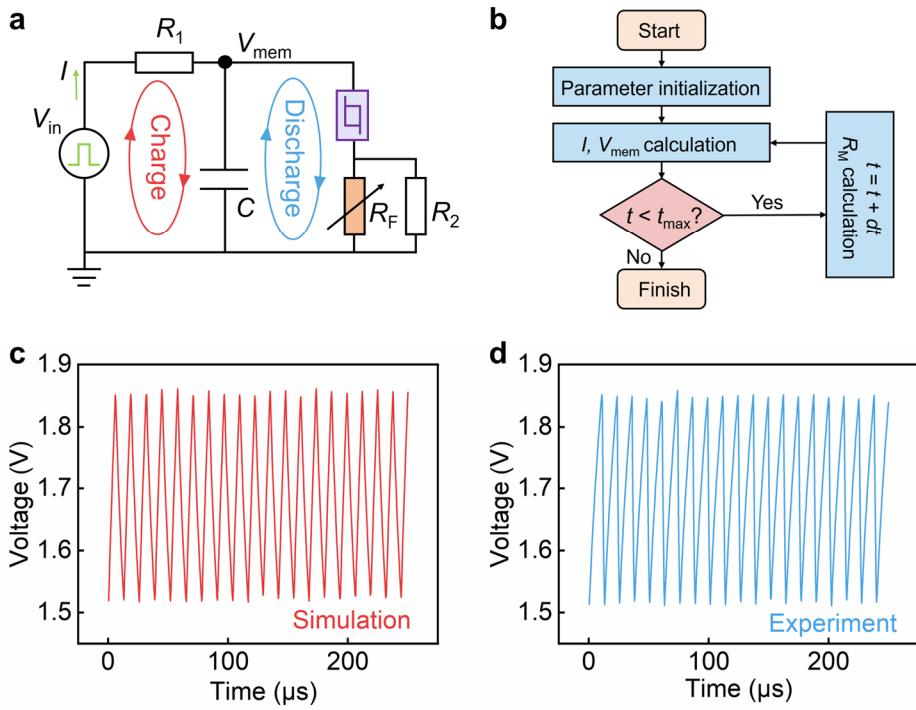

36 **Supplementary Note 2. Memristor model and circuit simulation.**

37 The generation of oscillatory signals primarily arise from the charging and discharging behaviors of the capacitor

38 induced by the resistive switching of the NbO<sub>x</sub> memristor. The operating mechanism of the MMN is illustrated in

39 Supplementary Fig. 6a. Based on the previous circuit analysis, a model is established using the finite difference method

40 as follows:

41

$$R_0 = R_{F2} \parallel R_2 \quad (1)$$

42

$$I(t) = \frac{V_{in} - V_{mem}(t)}{R_1} \quad (2)$$

43

$$V_{mem}(t + dt) = V_{mem}(t) + dt \frac{I(t) - \frac{V_{mem}(t)}{(R_M + R_0)}}{C} \quad (3)$$

44

$$R_M(t + dt) = \begin{cases} R_L, & \frac{V_{mem}(t) \times R_M(t)}{(R_M(t) + R_0)} \geq V_{th} \\ R_H, & \frac{V_{mem}(t) \times R_M(t)}{(R_M + R_0)} \leq V_{hold} \\ R_M(t), & \text{else} \end{cases} \quad (4)$$

45 Here,  $I(t)$ ,  $R_M(t)$  and  $V_{mem}(t)$  denote the total current, memristor resistance and capacitor voltage at time  $t$ , respectively.

46  $R_L$ ,  $R_H$ ,  $V_{th}$  and  $V_{hold}$  are parameters extracted from experimental data at different temperatures.  $dt$  represents the time

47 step, and  $t_{max}$  denotes the total simulation duration. Supplementary Fig. 6b illustrates the simulation workflow, while

48 Supplementary Fig. 6c and Supplementary Fig. 6d show the simulation curve and the measured curve, respectively.

49 **Supplementary Figure 6.** **a**, Operating mechanisms of the MMN. **b**, Flowchart of the circuit simulation. **c-d**, Simulated (c) and

50 experimental (d) oscillatory signals of the MMN.

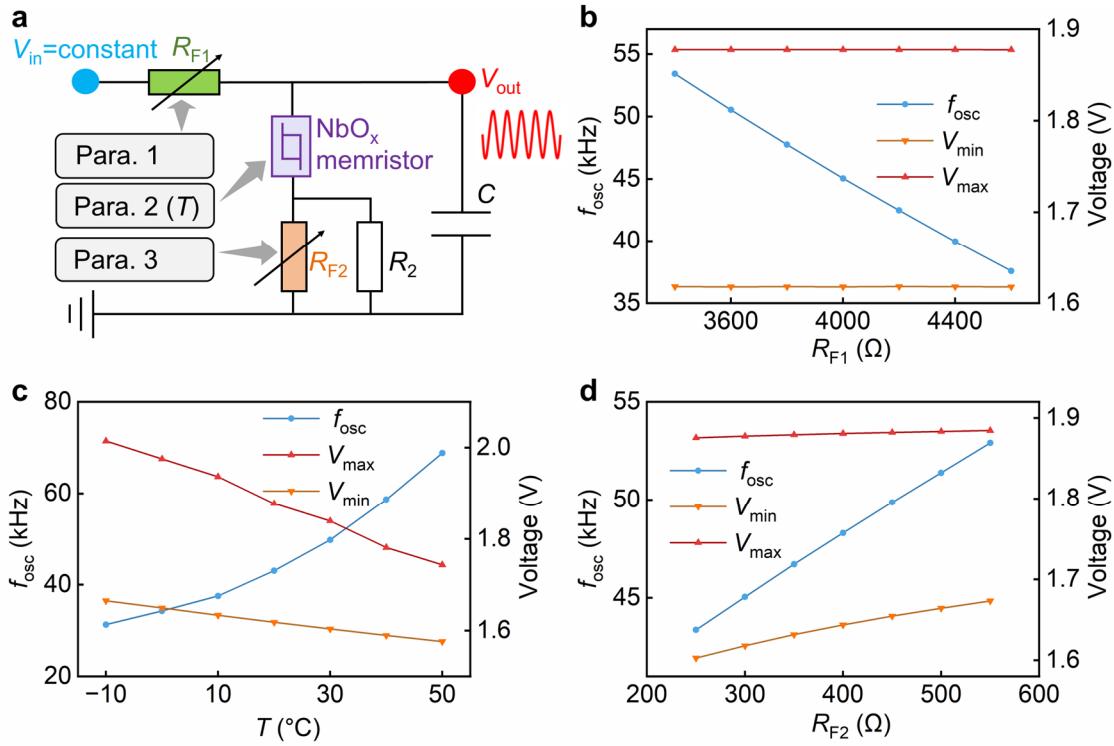

51 **Supplementary Note 3. Modified memristive multisensory neuron.**

52 For other combinations of physical modalities, the memristive multisensory neuron (MMN) can be modified for

53 applicability. Supplementary Fig. 7a shows the schematic of the modified MMN. By employing an  $\text{NbO}_x$  memristor

54 and two resistive sensors, the fusion of three physical modalities is achieved. The  $\text{NbO}_x$  memristor performs temperature

55 sensing, while the resistive sensor  $R_{F2}$  senses the second physical modality. The analysis of their effects on oscillatory

56 signals follows the same process as in the MMN. The third physical modality can be sensed using the resistive sensor

57  $R_{F1}$ . An increase in the resistance of  $R_{F1}$  slows down the capacitor charging and discharging process, resulting only in a

58 reduction of  $f_{\text{osc}}$ . Therefore, the circuit can be described as follows:

59

$$V_{\text{max}} = \frac{R_{\text{H}} + (R_{F2} || R_2)}{R_{\text{H}}} V_{\text{th}} \quad (5)$$

60

$$V_{\text{min}} = \frac{R_{\text{L}} + (R_{F2} || R_2)}{R_{\text{L}}} V_{\text{hold}} \quad (6)$$

61

$$t_{\text{r}} = CR_{\text{HO}} \ln \left( \frac{V_{\text{in}} - \frac{R_{F1}}{R_{\text{HO}}} V_{\text{min}}}{V_{\text{in}} - \frac{R_{F1}}{R_{\text{HO}}} V_{\text{max}}} \right) \quad (7)$$

62

$$t_{\text{f}} = CR_{\text{LO}} \ln \left( \frac{V_{\text{in}} - \frac{R_{F1}}{R_{\text{LO}}} V_{\text{max}}}{V_{\text{in}} - \frac{R_{F1}}{R_{\text{LO}}} V_{\text{min}}} \right) \quad (8)$$

63

$$f_{\text{osc}} = \frac{1}{t_{\text{r}} + t_{\text{f}}} \quad (9)$$

64

$$R_{\text{HO}} = R_{F1} || (R_{\text{H}} + (R_{F2} || R_2)) \quad (10)$$

65

$$R_{\text{LO}} = R_{F1} || (R_{\text{L}} + (R_{F2} || R_2)) \quad (11)$$

66 Supplementary Fig. 7b-d present the circuit simulation results based on measured data. It can be observed that the

67 three physical modalities exert different and monotonic effects on the fused oscillatory signals, thereby enabling the

68 decoupling of the trimodal information.

69 **Supplementary Figure 7.** **a**, Circuit structure of the modified MMN capable of fusing trimodal information. The temperature

70 modality is sensed by the  $\text{NbO}_x$  memristor, while the other two modalities are sensed by resistive sensors. **b-d**, Simulated effects of

71  $R_{F1}$  (b),  $T$  (c) and  $R_{F2}$  (d) on features of oscillatory signals.

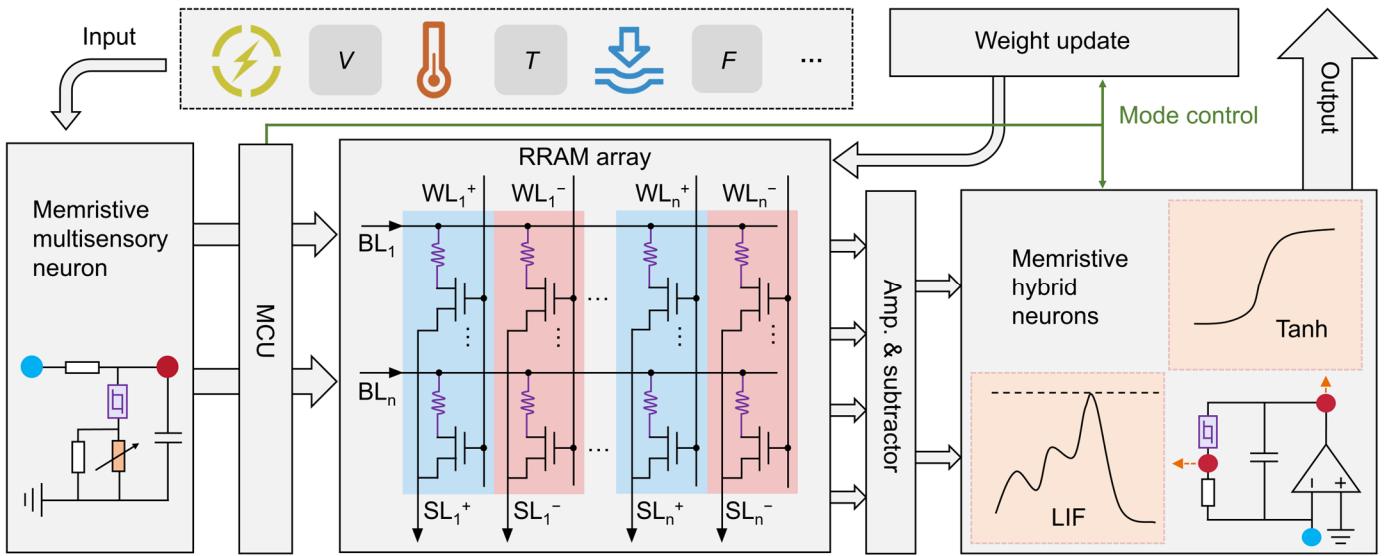

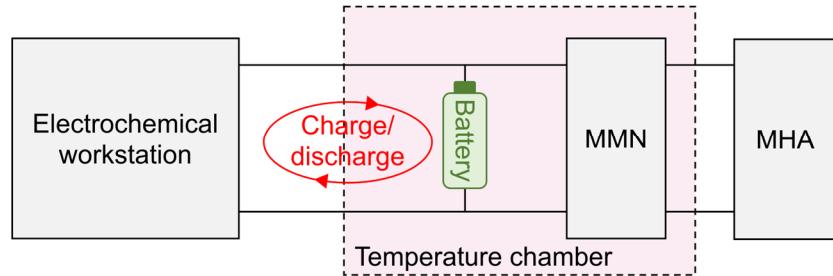

72 **Supplementary Figure 8.** Architecture of the proposed memristive perception system. The system consists of an MMN for trimodal

73 information fusion and an MHA for adaptive computation. This MHA integrates a RRAM array chip and MHNs. The MCU controls

74 the weight update and the working mode of neurons to achieve in-situ switching of the network architectures.

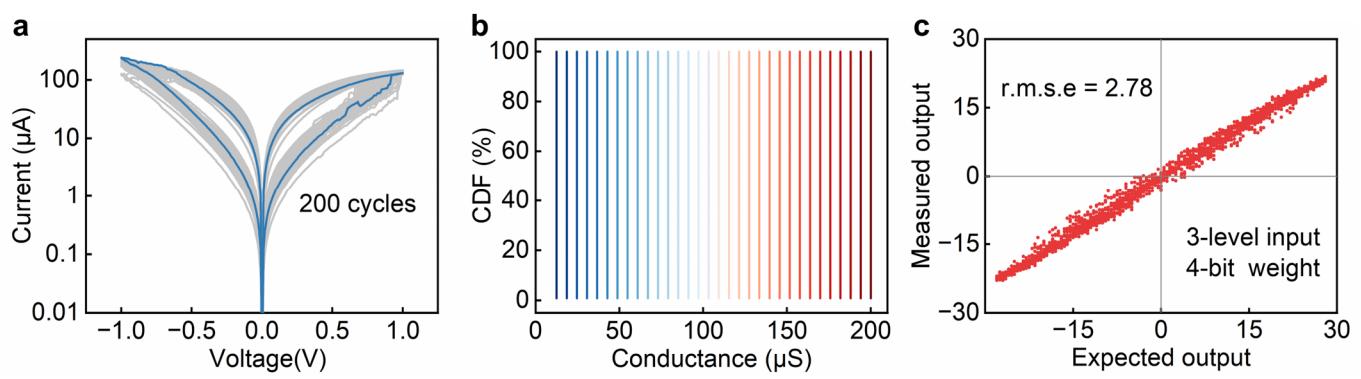

75 **Supplementary Note 4. Performance of the RRAM array.**

76 The resistive switching characteristics of the 1T1R cell exhibit excellent cycle-to-cycle consistency over 200 cycles

77 (Supplementary Fig. 9a). Under pulsed operation, the devices demonstrate reliable 5-bit storage resolution across a

78 range from 12.5  $\mu$ S to 200  $\mu$ S (Supplementary Fig. 9b). We also evaluated the matrix-vector multiplication (MVM)

79 performance, which is critical for neural network computation. Supplementary Fig. 9c shows the measured output with

80 3-level inputs and 4-bit weights.

81 **Supplementary Figure 9.** **a**, Switching characteristics of the 1T1R cell over 200 cycles. **b**, Cumulative probability distribution of

82 conductance (5 bits). **c**, MVM performance of the 1-Mb array.

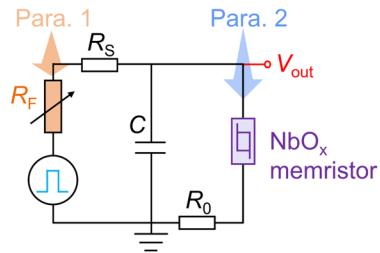

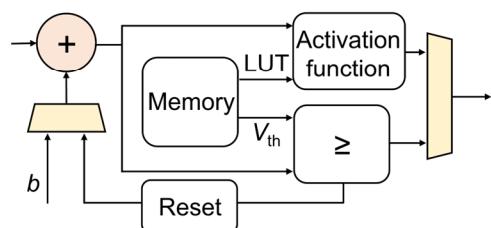

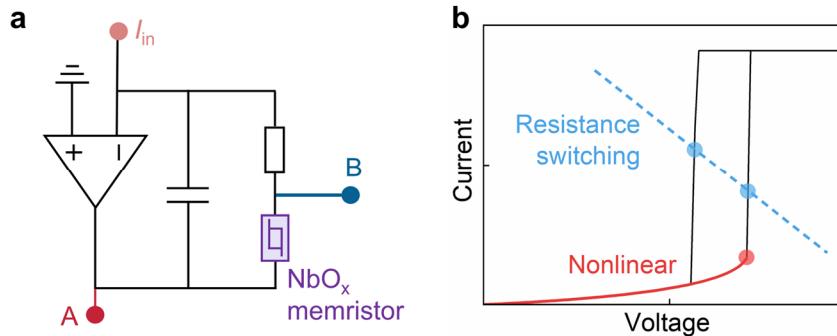

83 **Supplementary Note 5. Principle of functional reconfiguration in the memristive hybrid neuron.**

84 The circuit diagram of the memristive hybrid neuron (MHN) and the operating points of the  $\text{NbO}_x$  memristor for

85 different functions are shown in the Supplementary Fig. 10. When the input current is relatively low, the  $\text{NbO}_x$  memristor

86 operates in the high-resistance state, where the nonlinear resistance of the device leads to an approximately exponential

87 current-voltage relationship (as indicated by the red line). Since the resistance of the  $\text{NbO}_x$  memristor in the HRS is

88 much larger than that of the series resistor, the absolute value of the output at point A approximates the voltage across

89 the  $\text{NbO}_x$  memristor, thereby realizing the conversion from input current to output voltage to implement the Tanh

90 function. As the input current increases, the feedback loop of the operational amplifier can be regarded as an oscillation

91 circuit, where the  $\text{NbO}_x$  memristor switches between HRS and LRS (as indicated by the blue line), thereby generating

92 spike signals at point B to realize the LIF function.

93

94 **Supplementary Figure 10. a,** Circuit diagram of the MHN. **b,** Operating points of the  $\text{NbO}_x$  memristor for different functions.

95 Tanh activation function is realized through high-resistance nonlinearity and negative differential resistance of the  $\text{NbO}_x$  memristor,

96 while the LIF behavior is enabled by threshold switching characteristics of the device.

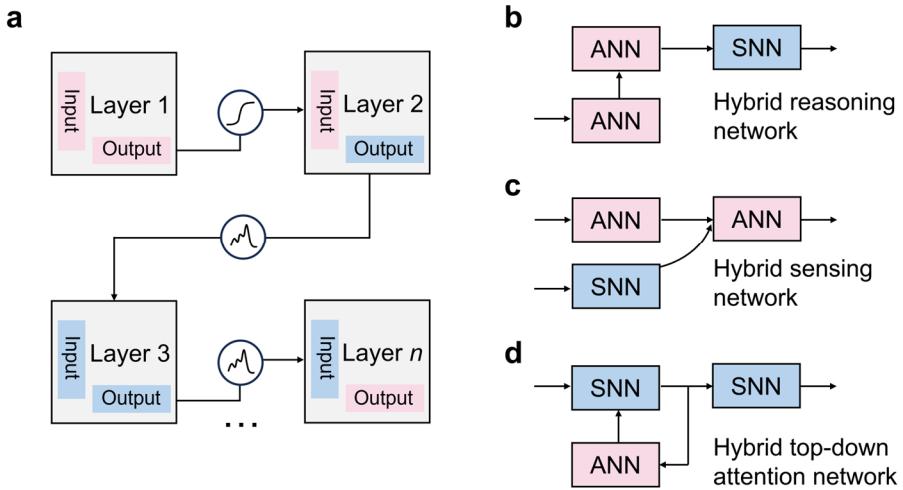

97 **Supplementary Figure 11. a**, Flexible interlayer connection topology. Each layer can be in-situ converted between ANN and SNN

98 modes, thereby enabling flexible implementation of arbitrary network topologies. **b-d**, HNNs with series (b), parallel (c) and

99 feedback (d) architectures. The serial structure enables multi-stage reasoning using different networks to progressively extract

100 hierarchical features<sup>1</sup>. The parallel structure employs multiple specialized networks to perform customized processing of specific

101 sensing data sources<sup>2</sup>. The feedback structure leverages high-level outputs to regulate front-end networks, where attention

102 modulation endows it with strong adaptive capability<sup>3</sup>.

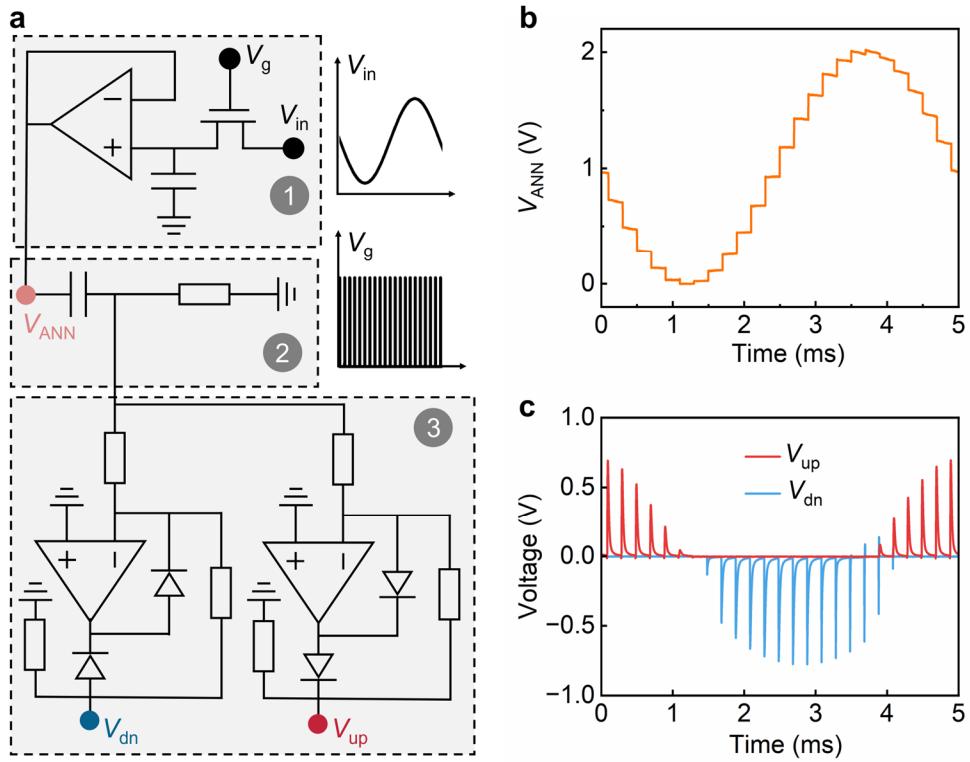

103 **Supplementary Figure 12.** **a**, Circuit structure of the general encoding unit (GEU). **b-c**, Experimental results for ANN (b) and

104 SNN (c) when a sine wave is applied into the circuit.

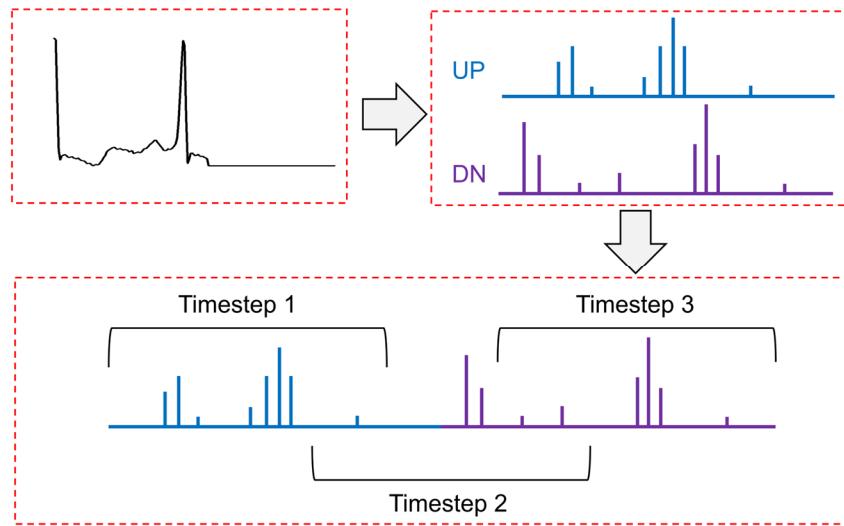

105 **Supplementary Figure 13.** Data acquisition and segmentation of the ECG data. The ECG data are encoded into UP and DN spike

106 sequences. The 187-slot data from two sequences are aggregated into 374 slots, which are then grouped by three overlapped

107 windows and fed into SNN as spike inputs over three timesteps.

108 **Supplementary Note 6. Network simulation of the ECG classification task.**

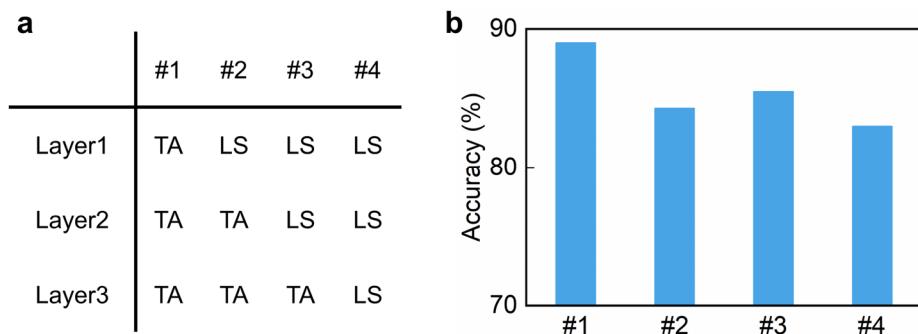

109 Benefiting from the in-situ reconfigurability of the MHN, different network architectures can be realized under the same

110 hardware configuration. We first investigate the performance of three-layer networks with different compositions using

111 the spatiotemporal backpropagation training algorithm (Supplementary Fig. 14a). As shown in Supplementary Fig. 14b,

112 the simulation results indicate that the 2LS-1TA HNN slightly outperforms the 1LS-2TA HNN (LS denotes the LIF

113 neuron configuration and TA denotes the Tanh function configuration). Therefore, ANN, 2LS-1TA HNN and SNN are

114 subsequently deployed on the MHA for further experiments. Details of the network dimensions are provided in

115 Supplementary Table 4.

116 **Supplementary Figure 14.** **a**, Details of three-layer HNNs with different compositions. **b**, Their corresponding inference accuracies.

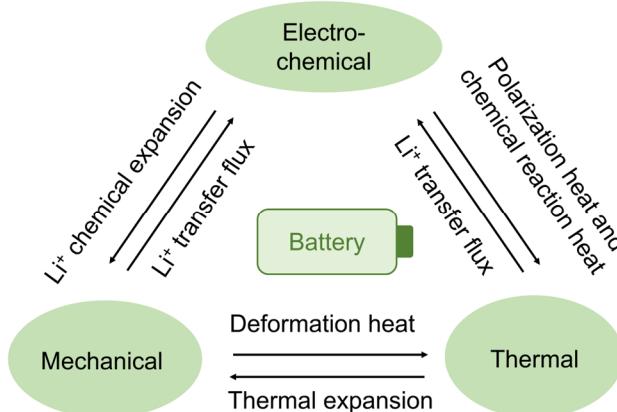

117 **Supplementary Note 7. Electro-thermo-mechanical coupled behaviors of a battery**

118 Electrochemical reactions inside the battery cause expansion and contraction of the anode/cathode electrodes, and the

119 resulting volume changes induce stress variations that further affect electrochemical behavior. Both electrochemical

120 processes (e.g., reaction-induced heat) and mechanical processes (e.g., deformation-induced heat) generate thermal

121 effects. Moreover, battery performance is highly sensitive to ambient temperature: thermal factors not only influence

122 electrochemical kinetics but also induce thermal stress. Therefore, battery exhibits complex thermo-mechanical

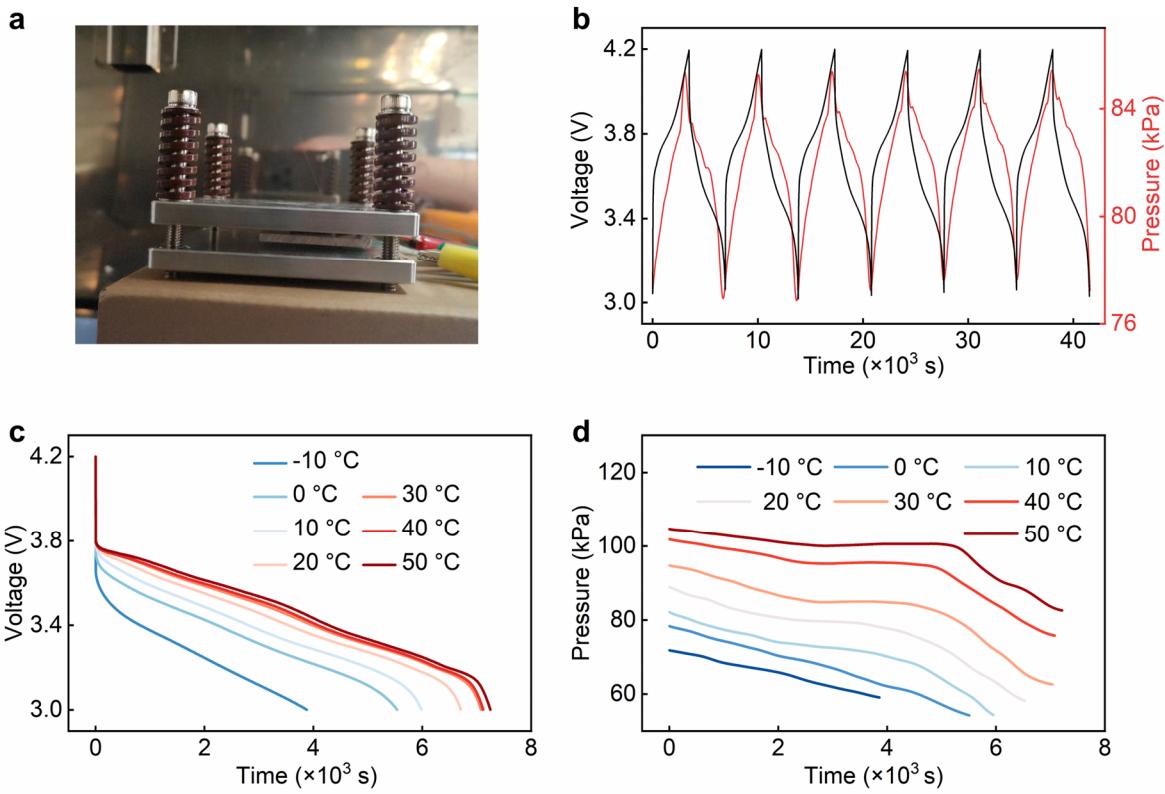

123 coupling behaviors<sup>4</sup> (Supplementary Fig. 15). Supplementary Fig. 16a shows the experimental setup, including the

124 battery, pressure sensor and fixture. This setup enables direct monitoring of the variations in physical parameters during

125 the battery charging and discharging processes. Supplementary Fig. 16b illustrates the evolution of voltage and stress

126 under isothermal charge-discharge cycling. To further investigate the effects of thermal factors, the voltage and stress

127 during the discharge process under different temperature conditions are recorded. Supplementary Fig. 16c-d show the

128 corresponding curves of battery voltage and stress.

129

130 **Supplementary Figure 15.** Complex thermo-mechanical coupling behaviors of battery.

131

132 **Supplementary Figure 16.** **a**, Experimental setup comprising a battery, pressure sensor and fixture. **b**, Evolution of battery voltage

133 and stress under cyclic charge-discharge operation. **c-d**, Battery voltage (c) and stress (d) curves during the discharge process across

134 different temperatures.

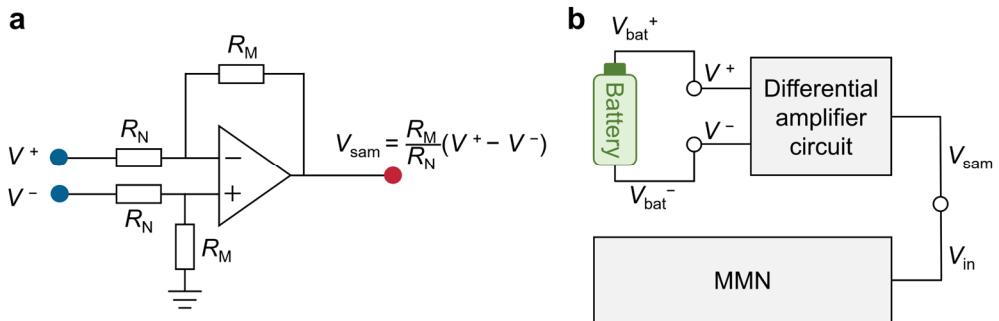

135 **Supplementary Figure 17. a**, Differential amplifier circuit. **b**, Connection diagram of the differential amplifier circuit with the

136 battery and the MMN.

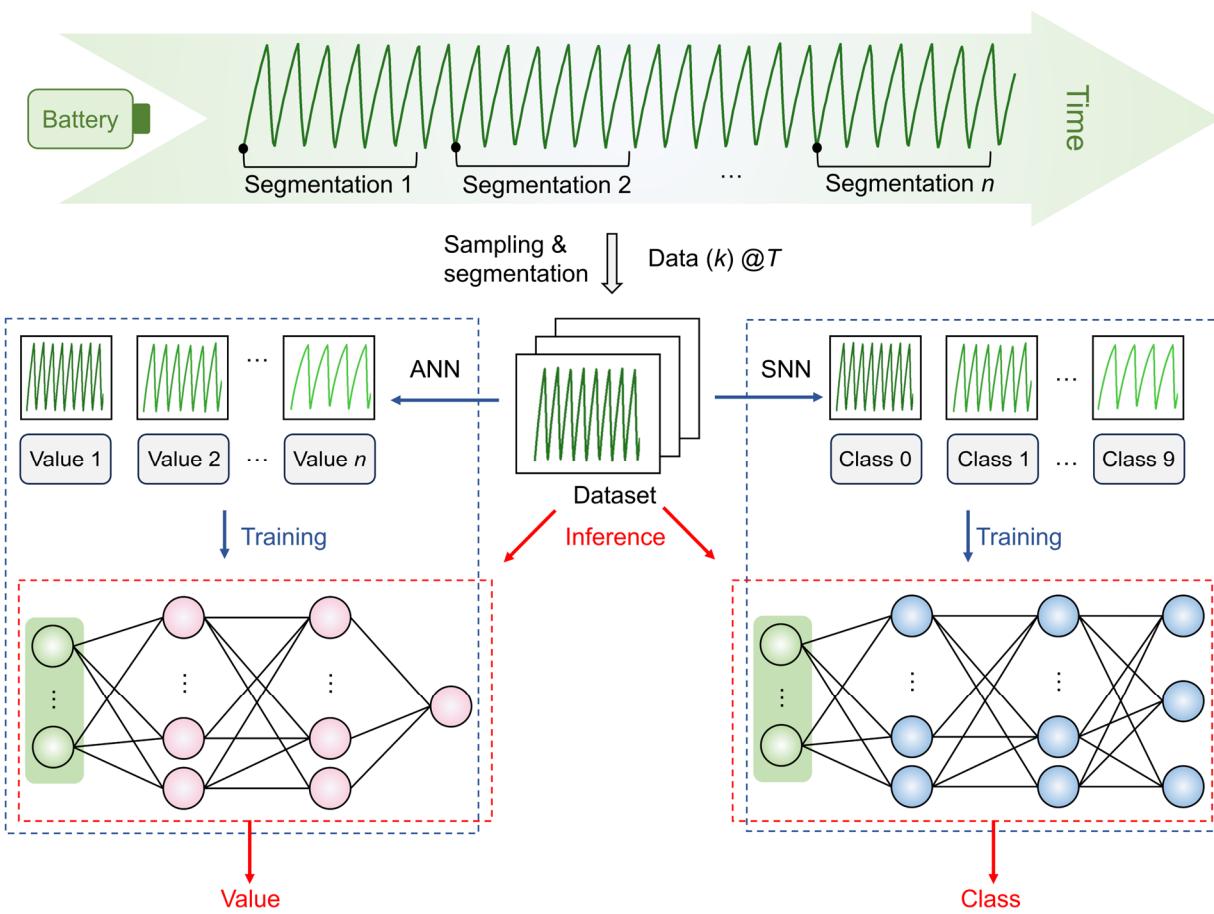

137 **Supplementary Figure 18.** Schematic diagram of SOC estimation workflow in ANN and SNN modes. Raw data are sampled and

138 segmented into dataset for task-specific training and inference. In ANN mode, SOC values are directly used for training, while in

139 SNN mode, the dataset is partitioned into ten classes representing different SOC ranges.

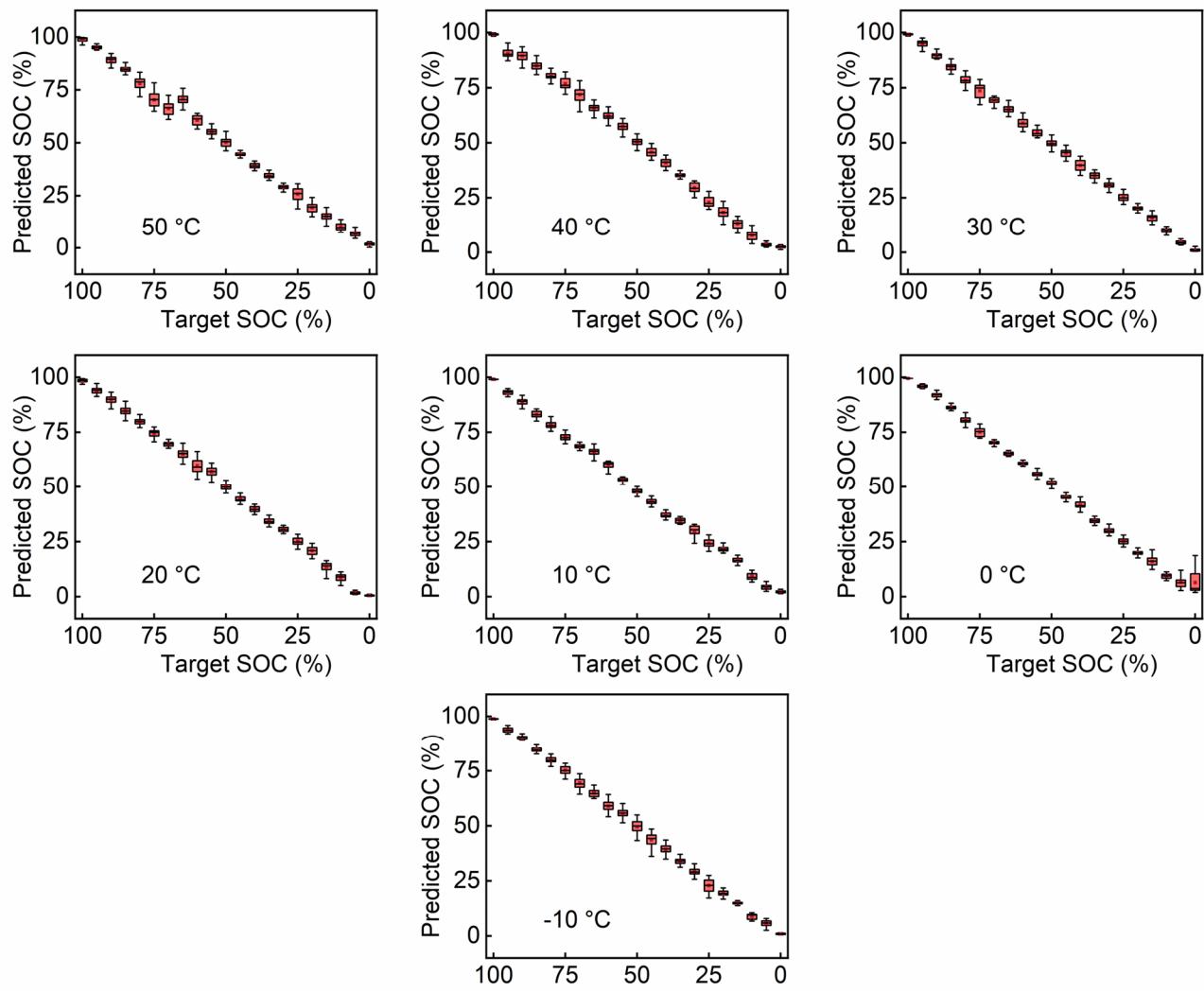

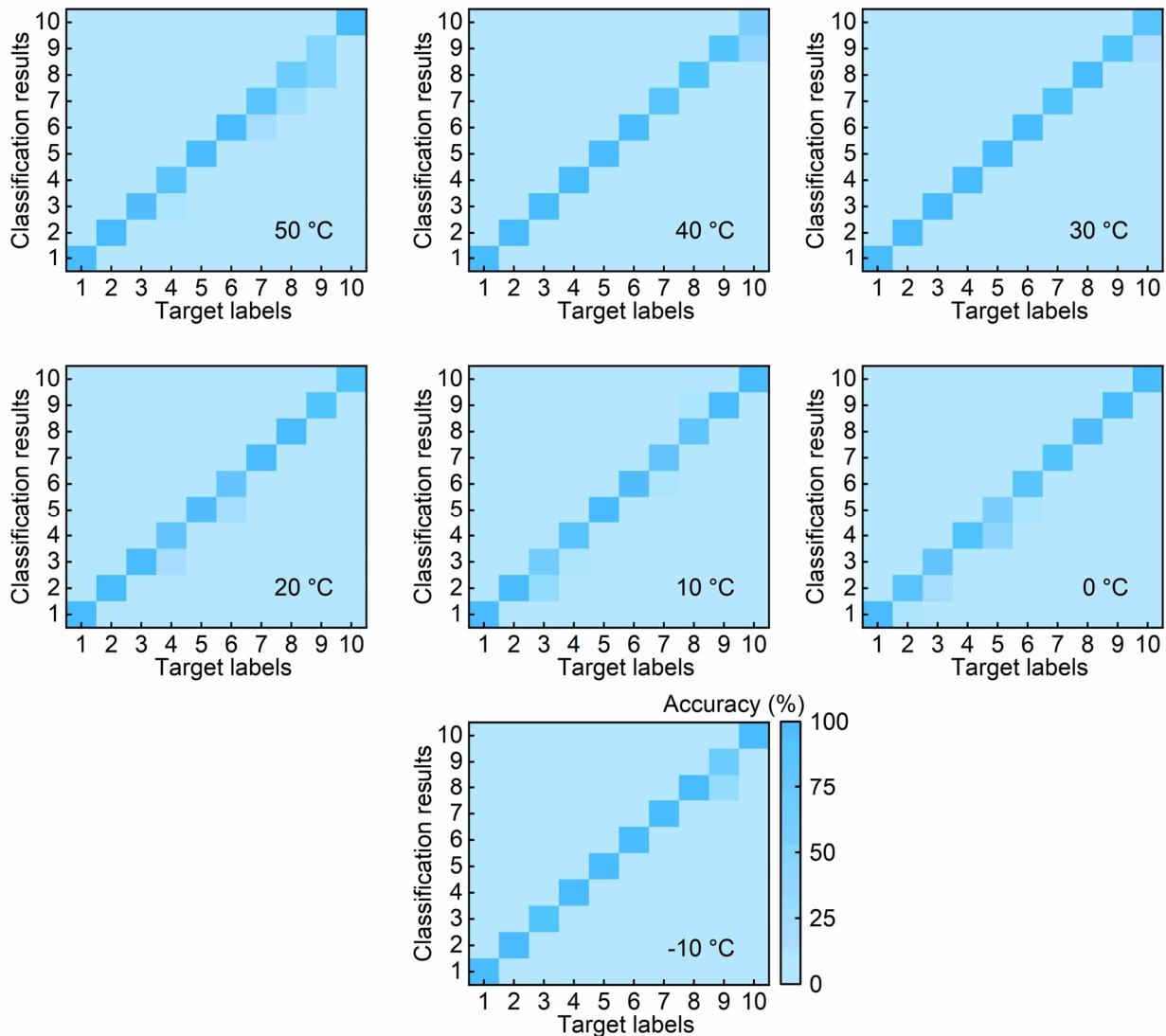

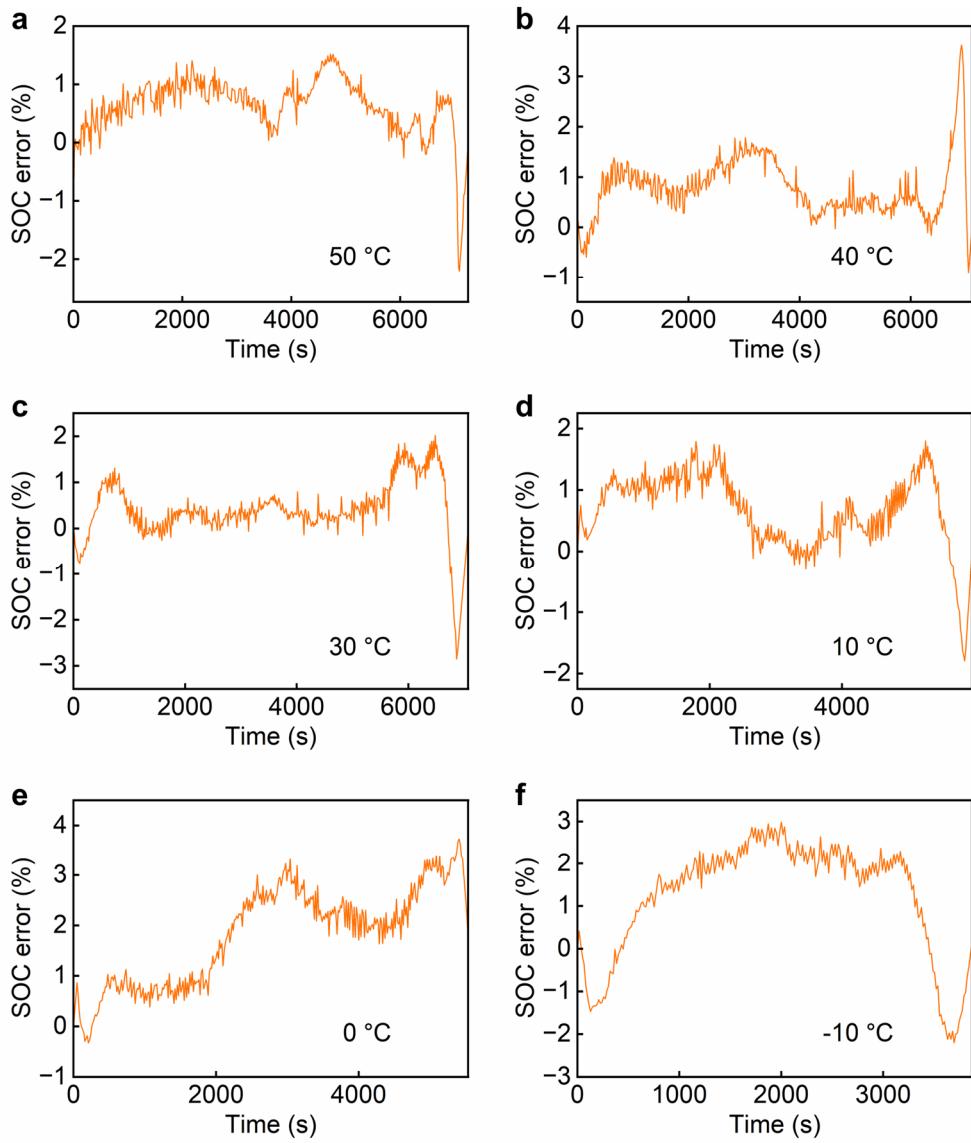

140 **Supplementary Note 8. Detailed results of system operation.**

141 Since the dataset contains test data across seven different temperatures, the system can achieve SOC estimation over a

142 wide temperature range. When divided by temperature, the statistical results of ANN and SNN modes are shown in

143 Supplementary Fig. 19 and Supplementary Fig. 20. Under the same hardware configuration, switching between ANN

144 and SNN modes is realized, with the corresponding weight distributions presented in Supplementary Fig. 21 and

145 Supplementary Fig. 22. To further analyze the system performance, the dataset is expanded based on measured data.

146 Simulations are conducted to obtain the system outputs during the discharge process at intervals of 16 s. This dataset is

147 then used to train the system in ANN mode. As shown in Supplementary Fig. 23, the system achieves SOC estimation

148 throughout the full discharge process over a wide temperature range.

149

**Supplementary Figure 19.** Distribution of the estimated SOC values at 50 °C (a), 40 °C (b), 30 °C (c), 20 °C (d), 10 °C (e), 0 °C

150

(f) and -10 °C (g).

151 **Supplementary Figure 20.** Confusion matrix of the classification results at 50 °C (a), 40 °C (b), 30 °C (c), 20 °C (d), 10 °C (e),

152 0 °C (f) and -10 °C (g).

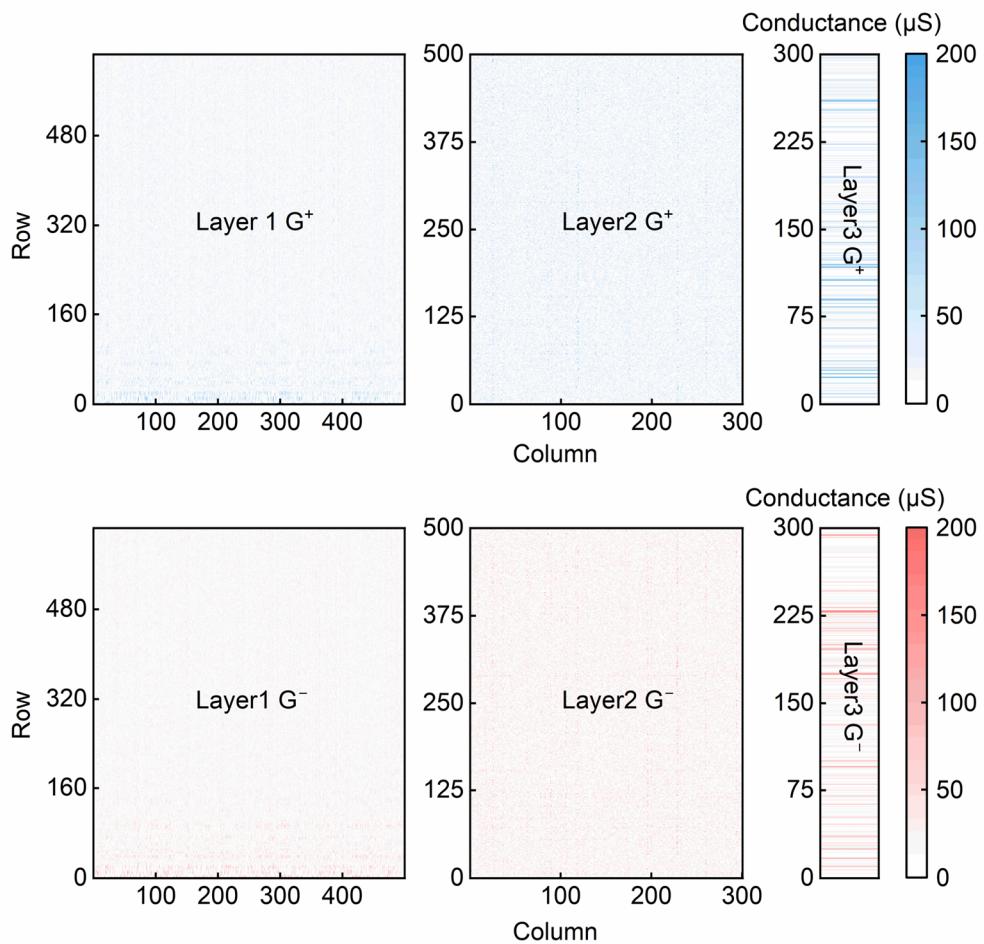

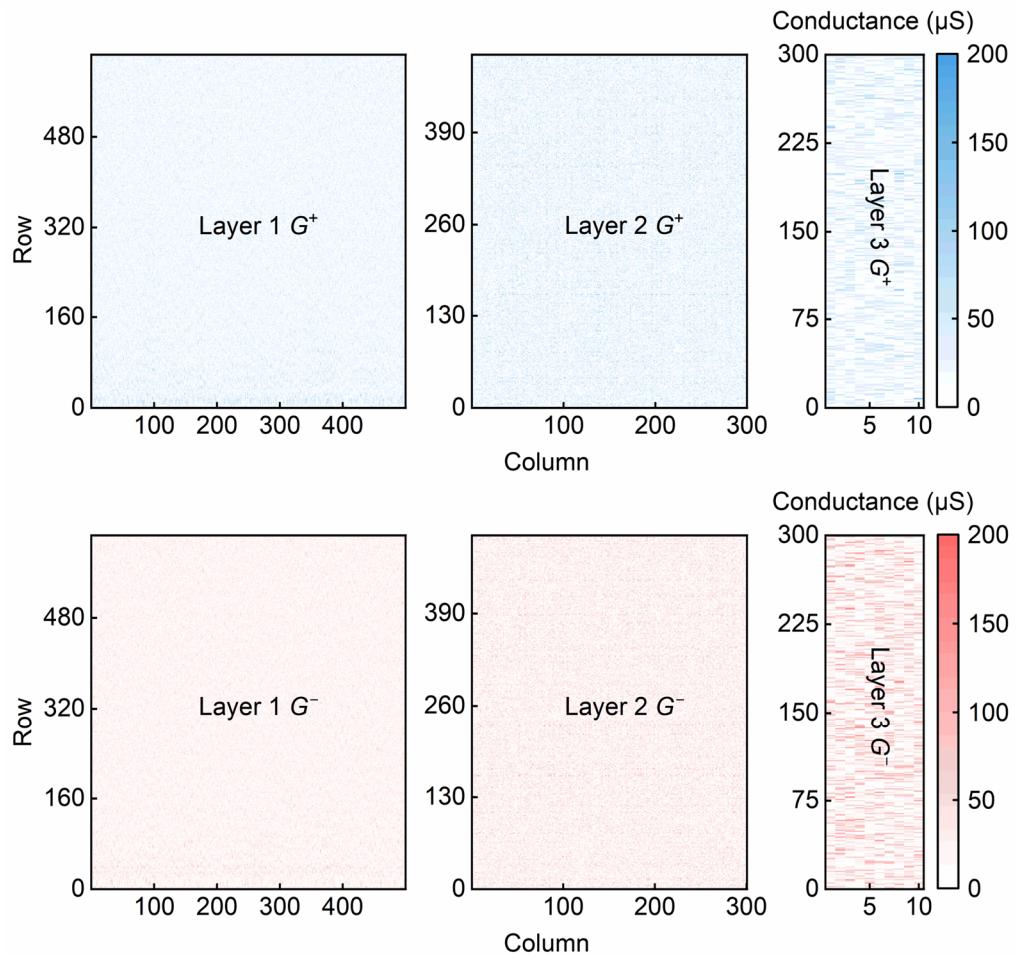

153 **Supplementary Figure 21.** Measured 5-bit weights of ANN written into the RRAM array, shown as the positive and negative

154 conductance maps of three layers.

155 **Supplementary Figure 22.** Measured 5-bit weights of SNN written into the RRAM array, shown as the positive and negative

156 conductance maps of three layers.

158 **Supplementary Figure 24.** Illustration of the testing setups.

159

**Supplementary Table 1.** Comparison with previous state-of-the-art sensing neurons.

| Ref.               | 2022<br>Nat. Commun. <sup>5</sup>          | 2023<br>IEDM <sup>6</sup>             | 2024<br>Nat. Commun. <sup>7</sup>   | This work                            |

|--------------------|--------------------------------------------|---------------------------------------|-------------------------------------|--------------------------------------|

| Technology         | Sensor<br>+VO <sub>2</sub>                 | Photo-transistor<br>+NbO <sub>x</sub> | Pressure sensor<br>+VO <sub>2</sub> | Pressure sensor<br>+NbO <sub>x</sub> |

| Fusion             | ✗                                          | ✗                                     | ✓                                   | ✓                                    |

| Sensory signals    | <i>T</i> or <i>F</i> or light or curvature | Optical                               | <i>T</i> & <i>F</i>                 | <i>V</i> & <i>T</i> & <i>F</i>       |

| Processing method  | SNN                                        | SNN                                   | Spiking reservoir network           | HNN                                  |

| Energy consumption | 2.9 nJ/spike                               | ~0.1 nJ/spike                         | 3.9-50 nJ/spike                     | ~5.1 nJ/spike                        |

160

161

**Supplementary Table 2.** Comparison with previous state-of-the-art HNN accelerators.

| Ref.             | 2020<br>JSSC <sup>8</sup> | 2022<br>ISSCC <sup>9</sup> | 2023<br>ISSCC <sup>10</sup> | 2024<br>JSSC <sup>11</sup> | This work                                        |

|------------------|---------------------------|----------------------------|-----------------------------|----------------------------|--------------------------------------------------|

| Technology       | 28 nm<br>SRAM             | 180 nm<br>SRAM             | 28 nm<br>SRAM               | 28 nm<br>SRAM              | 40 nm TaO <sub>x</sub> RRAM<br>+NbO <sub>x</sub> |

| Implementation   | Digital                   | Mixed-signal               | Digital                     | Digital                    | Mixed-signal                                     |

| Weight precision | 8-bit                     | 4-bit                      | 4-, 8-bit                   | 1-, 2-, 4-, 8-bit          | 4-, 5-bit                                        |

| Network          | SNN/ANN                   | SNN                        | SNN/CNN                     | SNN/ANN                    | SNN/ANN                                          |

| Neuron           | Distinct                  | Single                     | Distinct                    | Distinct                   | Hybrid                                           |

| CIM technology   | ✗                         | ✓                          | ✗                           | ✗                          | ✓                                                |

162

163 **Supplementary Table 3.** Parameters of the MMN and MHN.

|     |       |              |

|-----|-------|--------------|

| MMN | $R_1$ | 4 k $\Omega$ |

|     | $R_2$ | 500 $\Omega$ |

|     | $C$   | 10 nF        |

| MHN | $R$   | 50 $\Omega$  |

|     | $C$   | 10 nF        |

172 **Supplementary Table 4.** Programming conductance error under different modes.

| Task           | Mode | Layer 1          |                     | Layer 2          |                     | Layer 3          |                     |

|----------------|------|------------------|---------------------|------------------|---------------------|------------------|---------------------|

|                |      | $\mu$ ( $\mu$ S) | $\sigma$ ( $\mu$ S) | $\mu$ ( $\mu$ S) | $\sigma$ ( $\mu$ S) | $\mu$ ( $\mu$ S) | $\sigma$ ( $\mu$ S) |

| ECG<br>(4-bit) | HNN  | 1.29             | 1.36                | 1.34             | 1.52                | 1.31             | 1.48                |

| SOC<br>(5-bit) | ANN  | 0.777            | 1.01                | 0.776            | 0.964               | 0.930            | 1.57                |

|                | SNN  | 0.766            | 0.886               | 0.774            | 1.01                | 0.798            | 1.44                |

173 **Supplementary Table 5.** Network size.

| Task | Mode | Size                                  |

|------|------|---------------------------------------|

| ECG  | ANN  | $187 \times 300 \times 100 \times 5$  |

|      | HNN  | $187 \times 300 \times 100 \times 5$  |

|      | SNN  | $187 \times 300 \times 100 \times 5$  |

| SOC  | ANN  | $625 \times 500 \times 300 \times 1$  |

|      | SNN  | $625 \times 500 \times 300 \times 10$ |

174

175 **Reference**

- 176 1. Chancan, M., Hernandez-Nunez, L., Narendra, A., Barron, A. B. & Milford, M. A hybrid compact neural

177 architecture for visual place recognition. *IEEE Robot. Autom. Lett.* **5**, 993–1000 (2020).

- 178 2. Zhao, R. et al. A framework for the general design and computation of hybrid neural networks. *Nat.*

179 *Commun.* **13**, 3427 (2022).

- 180 3. Liu, F. & Zhao, R. Enhancing spiking neural networks with hybrid top-down attention. *Front. Neurosci.* **16**,

181 949142 (2022).

- 182 4. Yue, F. et al. A fully coupled electrochemical-mechanical-thermal model of all-solid-state thin-film Li-ion

183 batteries. *J. Power Sources* **539**, 231614 (2022).

- 184 5. Yuan, R. et al. A calibratable sensory neuron based on epitaxial VO<sub>2</sub> for spike-based neuromorphic

185 multisensory system. *Nat. Commun.* **13**, 3973 (2022).

- 186 6. Wang, R. et al. 1-phototransistor-1-threshold switching optoelectronic neuron for in-sensor compression

187 via spiking neuron network. In *2023 International Electron Devices Meeting (IEDM)* 1–4 (IEEE, 2023).

- 188 7. Li, Z. et al. Crossmodal sensory neurons based on high-performance flexible memristors for human-

189 machine in-sensor computing system. *Nat. Commun.* **15**, 7275 (2024).

- 190 8. Deng, L. et al. Tianjic: a unified and scalable chip bridging spike-based and continuous neural computation.

191 *IEEE J. Solid-State Circuits* **55**, 2228–2246 (2020).

- 192 9. Liu, Y. et al. An 82nW 0.53pJ/SOP clock-free spiking neural network with 40 µs latency for AIoT wake-up

193 functions using ultimate-event-driven bionic architecture and computing-in-memory technique. In *2022*

194 *IEEE International Solid- State Circuits Conference (ISSCC)* 372–374 (IEEE, 2022).

195 10. Kim, S. et al. C-DNN: a 24.5-85.8TOPS/W complementary-deep-neural-network processor with

196 heterogeneous CNN/SNN core architecture and forward-gradient-based sparsity generation. In *2023 IEEE*

197 *International Solid- State Circuits Conference (ISSCC)* 334–336 (IEEE, 2023).

198 11. Zhong, Y. et al. PAICORE: a 1.9-million-neuron 5.181-TSOPS/W digital neuromorphic processor with

199 unified SNN-ANN and on-chip learning paradigm. *IEEE J. Solid-State Circuits* **60**, 651–671 (2024).