**Supplementary Information:**

**Mechanism for reconfigurable logic in disordered dopant networks**

Henri Tertilt<sup>1</sup>, Jesse Bakker<sup>2</sup>, Marlon Becker<sup>1</sup>, Bram de Wilde<sup>2</sup>, Indrek Klanberg<sup>2</sup>,

Bernard J. Geurts<sup>3,4</sup>, Wilfred G. van der Wiel<sup>2,5</sup>, Andreas Heuer<sup>1</sup>, Peter A. Bobbert<sup>2,6</sup>

<sup>1</sup>*Institut für physikalische Chemie, Westfälische Wilhelms-Universität Münster, Münster, Germany*

<sup>2</sup>*NanoElectronics Group, MESA+ Institute for Nanotechnology,*

*and Center for Brain-Inspired Nano Systems (BRAINS),*

*University of Twente, Enschede, The Netherlands*

<sup>3</sup>*Multiscale Modeling and Simulation Group, Faculty of Electrical Engineering,*

*Mathematics and Computer Science, and Center for Brain-Inspired Nano Systems,*

*University of Twente, Enschede, The Netherlands*

<sup>4</sup>*Center for Computational Energy Research (CCER),*

*Eindhoven University of Technology, 5600 MB Eindhoven, The Netherlands*

<sup>5</sup>*Fachbereich Physik, Westfälische Wilhelms-Universität Münster, Münster, Germany*

<sup>6</sup>*Molecular Materials and Nanosystems Group and Center for Computational Energy Research,*

*Eindhoven University of Technology, Eindhoven, The Netherlands*

(Dated: August 9, 2021)

**CONTENTS**

|                                                                            |   |

|----------------------------------------------------------------------------|---|

| S1. Influence of number of counterdopants                                  | 2 |

| S2. Artificial evolution of Boolean logic in a second device               | 3 |

| S3. Boolean logic with shorter simulation time                             | 4 |

| S4. Voltage and current distributions for random control voltages          | 5 |

| S5. Voltage and current distributions for Boolean gates in a second device | 6 |

| S6. Correlations in output current for different logic inputs              | 7 |

| S7. Sensitivity of AND and XOR gates to $V_{c2}$ and $V_{c3}$              | 8 |

| S8. Gate abundances in a second device                                     | 9 |

| References                                                                 | 9 |

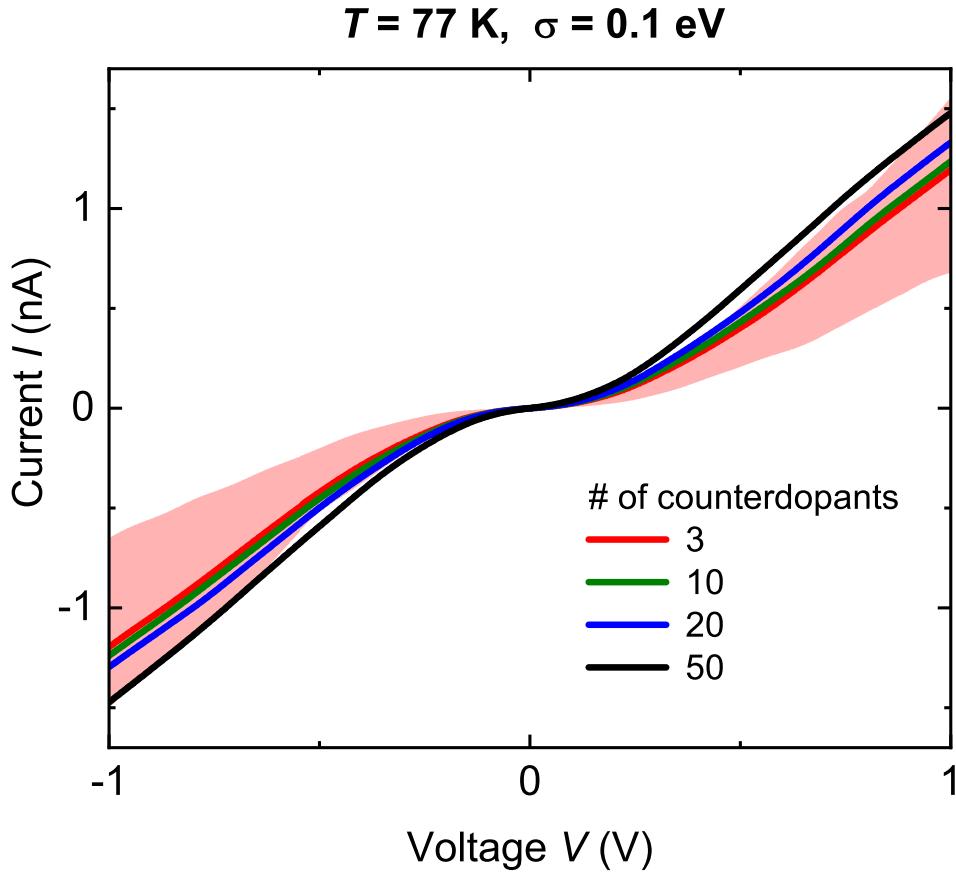

## S1. INFLUENCE OF NUMBER OF COUNTERDOPANTS

Figure S1. Simulated  $I$ - $V$  characteristics at 77 K and energy disorder strength  $\sigma = 0.1$  eV, averaged over the 8 neighbouring electrode combinations of 30 devices with different numbers of counterdopants. The result for 3 counterdopants is the same as in Fig. 1a of the main text, where half of the 240  $I$ - $V$  characteristics fall in the shaded red region. The averaged  $I$ - $V$  characteristic for 50 counterdopants (black line) still falls in this region.

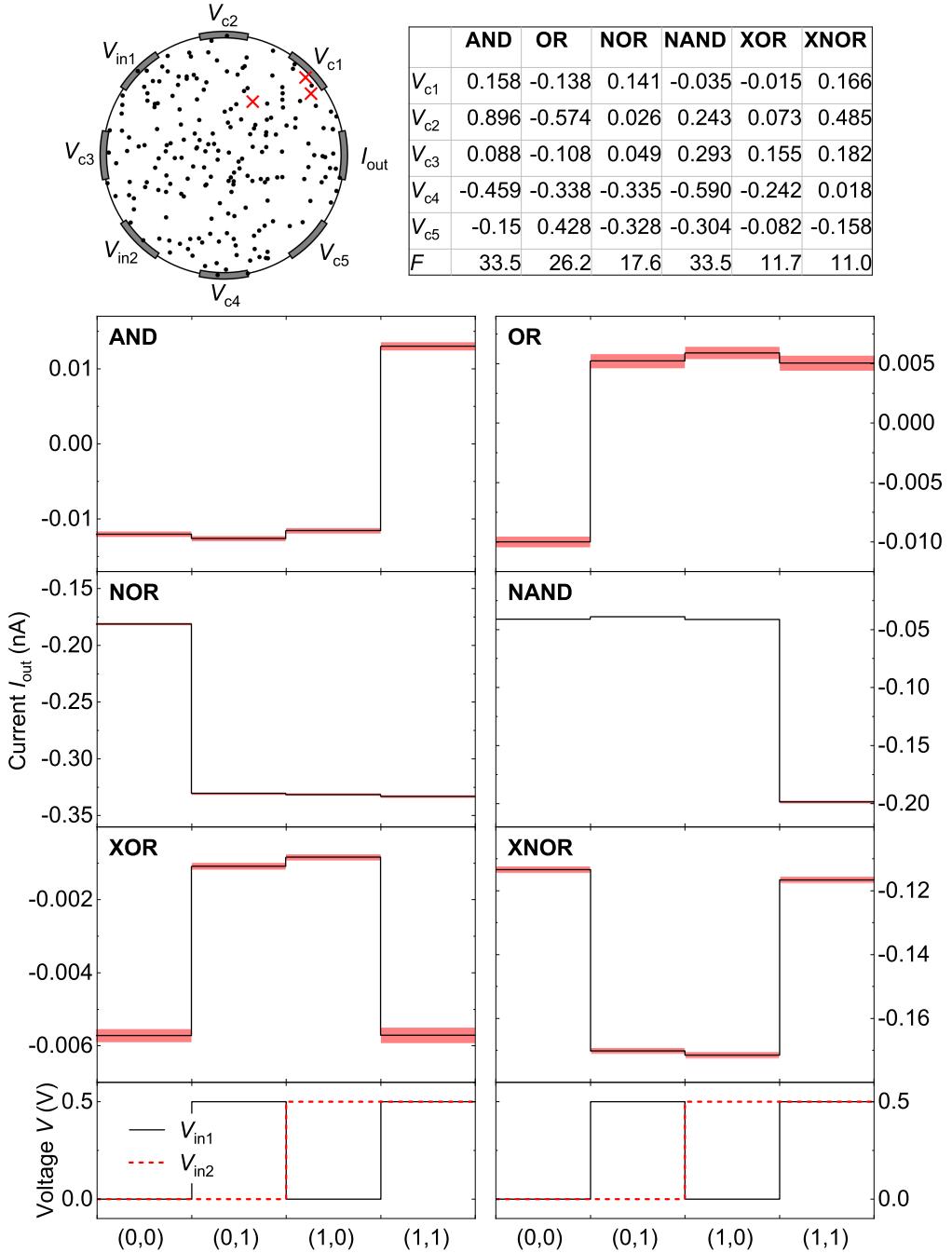

## S2. ARTIFICIAL EVOLUTION OF BOOLEAN LOGIC IN A SECOND DEVICE

Figure S2. Boolean functionality at 77 K as found by artificial evolution in the device shown at the top left, which is different from that in Fig. 2 of the main text. The control voltages  $V_{\text{c}1}$ – $V_{\text{c}5}$  and fitnesses  $F$  are given in the table at the top right.

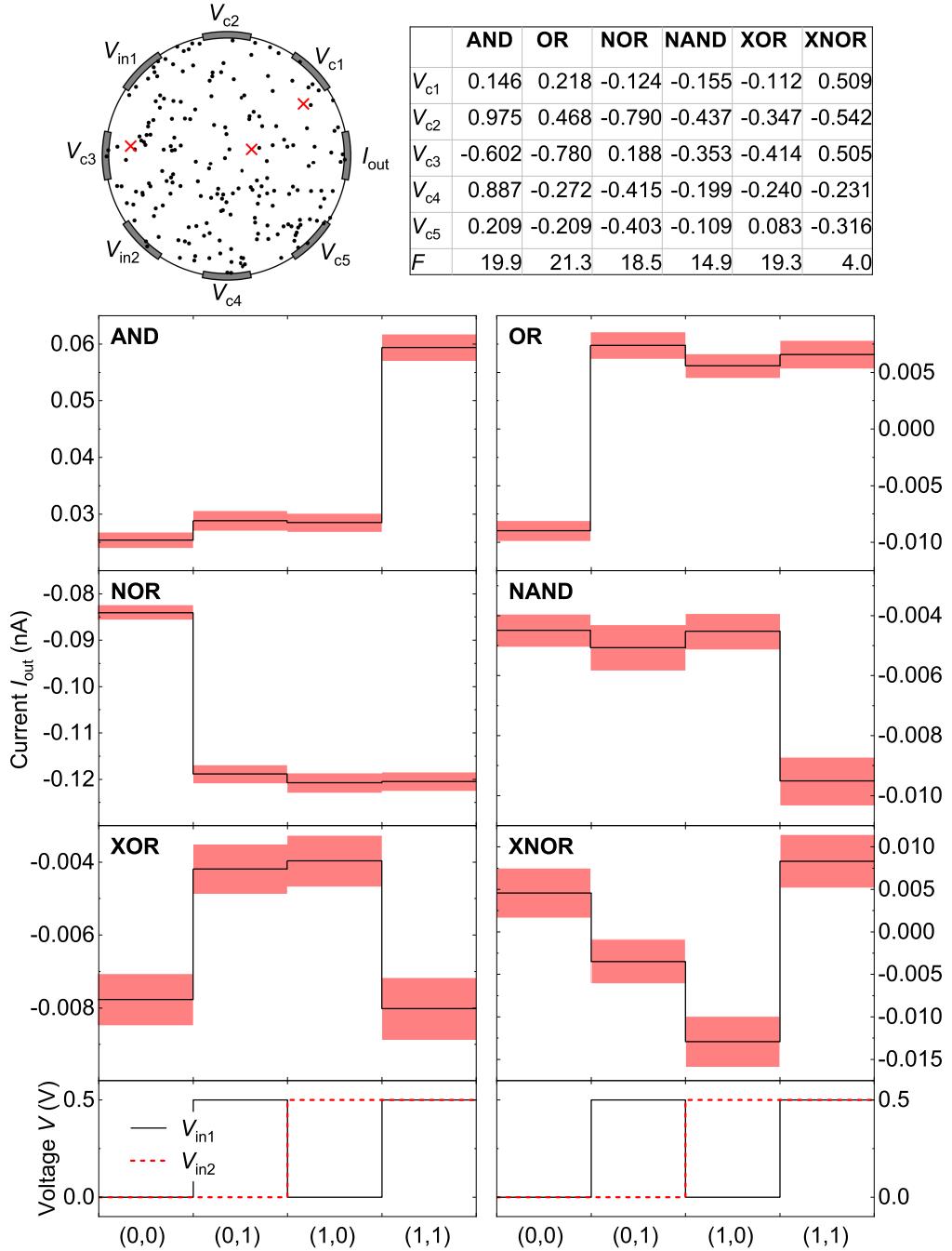

## S3. BOOLEAN LOGIC WITH SHORTER SIMULATION TIME

Figure S3. Same as in Fig. 2 of the main text, but with currents and uncertainties determined for  $10^6$  instead of  $10^7$  KMC steps. The control voltages  $V_{c1}$ – $V_{c5}$  are unchanged.

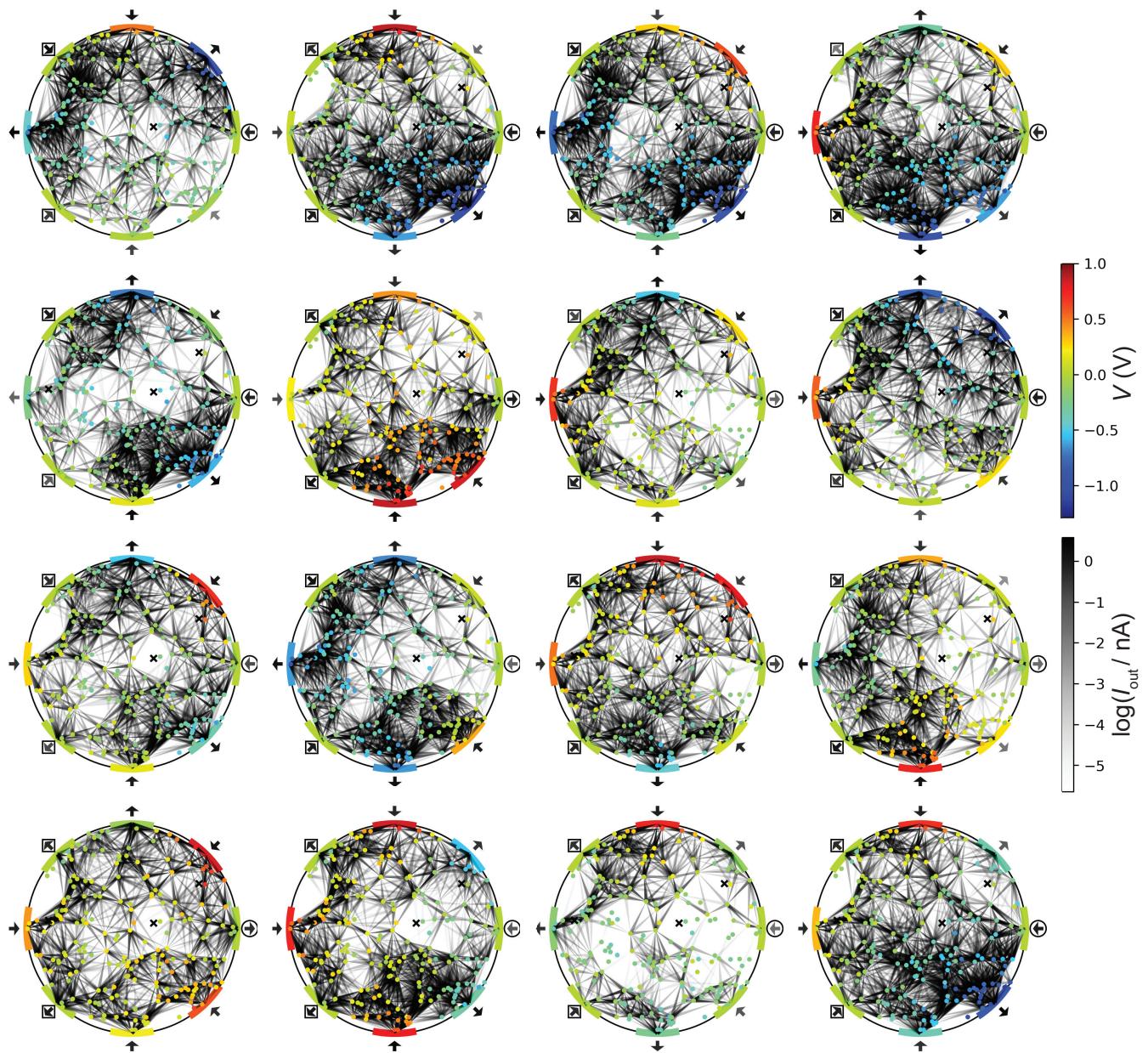

## S4. VOLTAGE AND CURRENT DISTRIBUTIONS FOR RANDOM CONTROL VOLTAGES

Figure S4. Voltages and currents for the device of Fig. 2 in the main text with 16 random control voltages in the interval  $[-1,1]$  V and  $(0,0)$  input.

## S5. VOLTAGE AND CURRENT DISTRIBUTIONS FOR BOOLEAN GATES IN A SECOND DEVICE

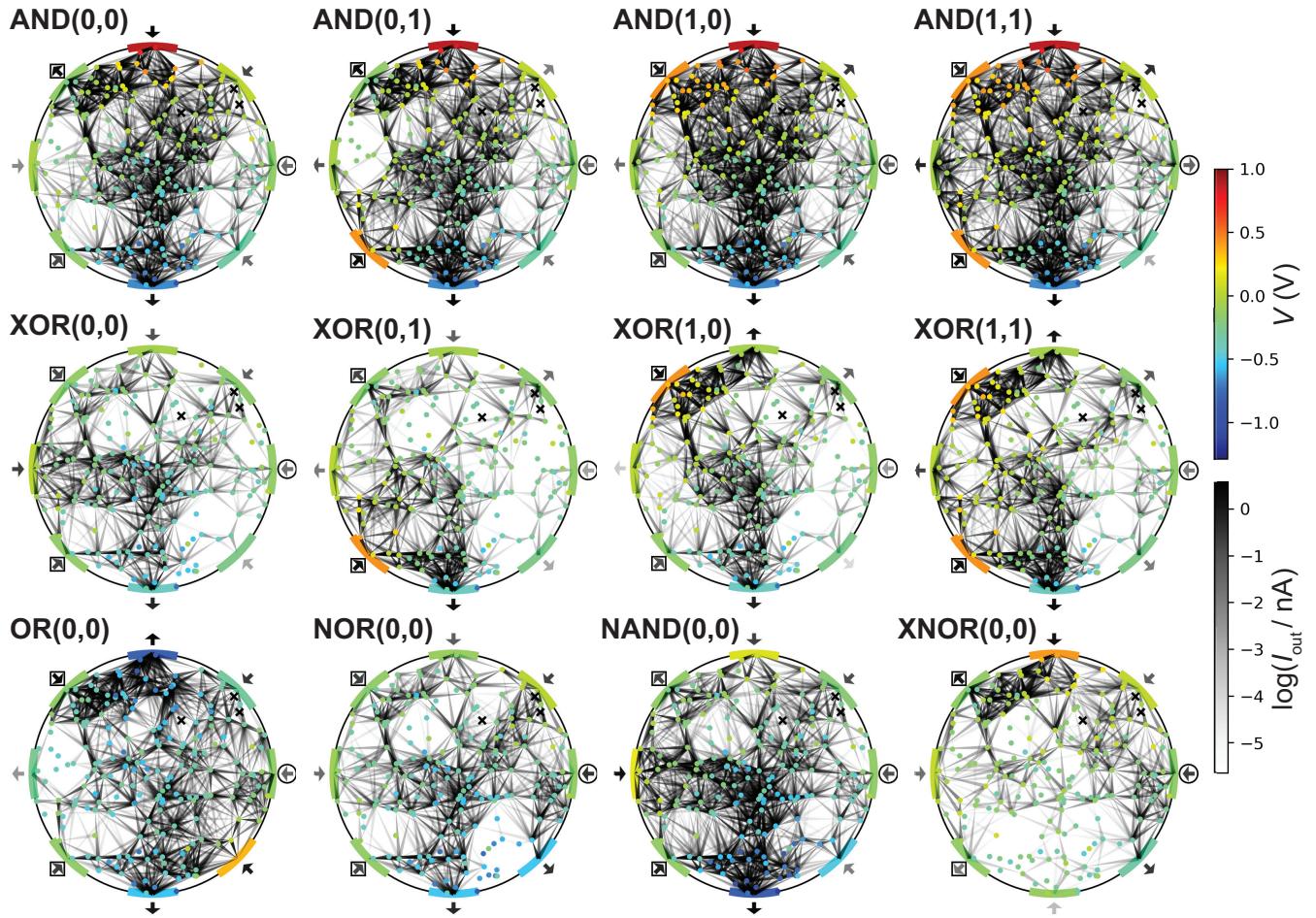

Figure S5. Voltages and currents for the device of Fig. S2. First row: AND gate for the four logic input combinations. Second row: XOR gate. Third row: OR, NOR, NAND, and XNOR gate with (0,0) input.

## S6. CORRELATIONS IN OUTPUT CURRENT FOR DIFFERENT LOGIC INPUTS

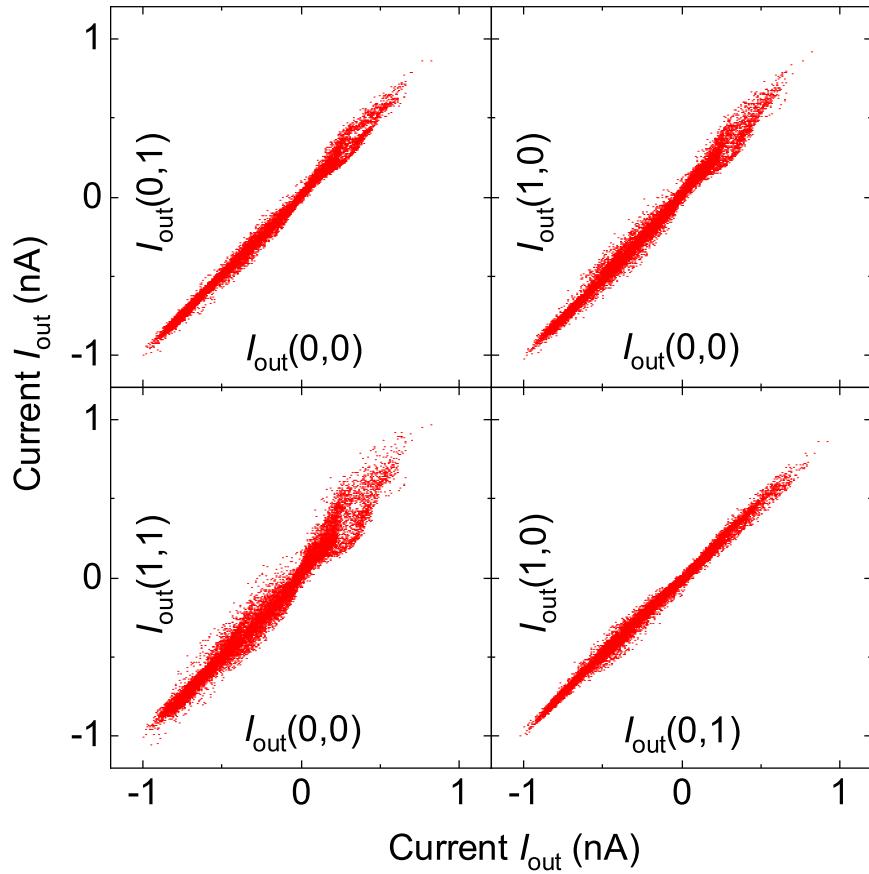

Figure S6. Correlations between current outputs of the device of Fig. 2 in the main text for logic inputs (0,0), (1,0), (0,1), and (1,1), and about 20,000 random combinations of the control voltages  $V_{c1}$ – $V_{c5}$  in the interval [−1,1] V.

**S7. SENSITIVITY OF AND AND XOR GATES TO  $V_{c2}$  AND  $V_{c3}$**

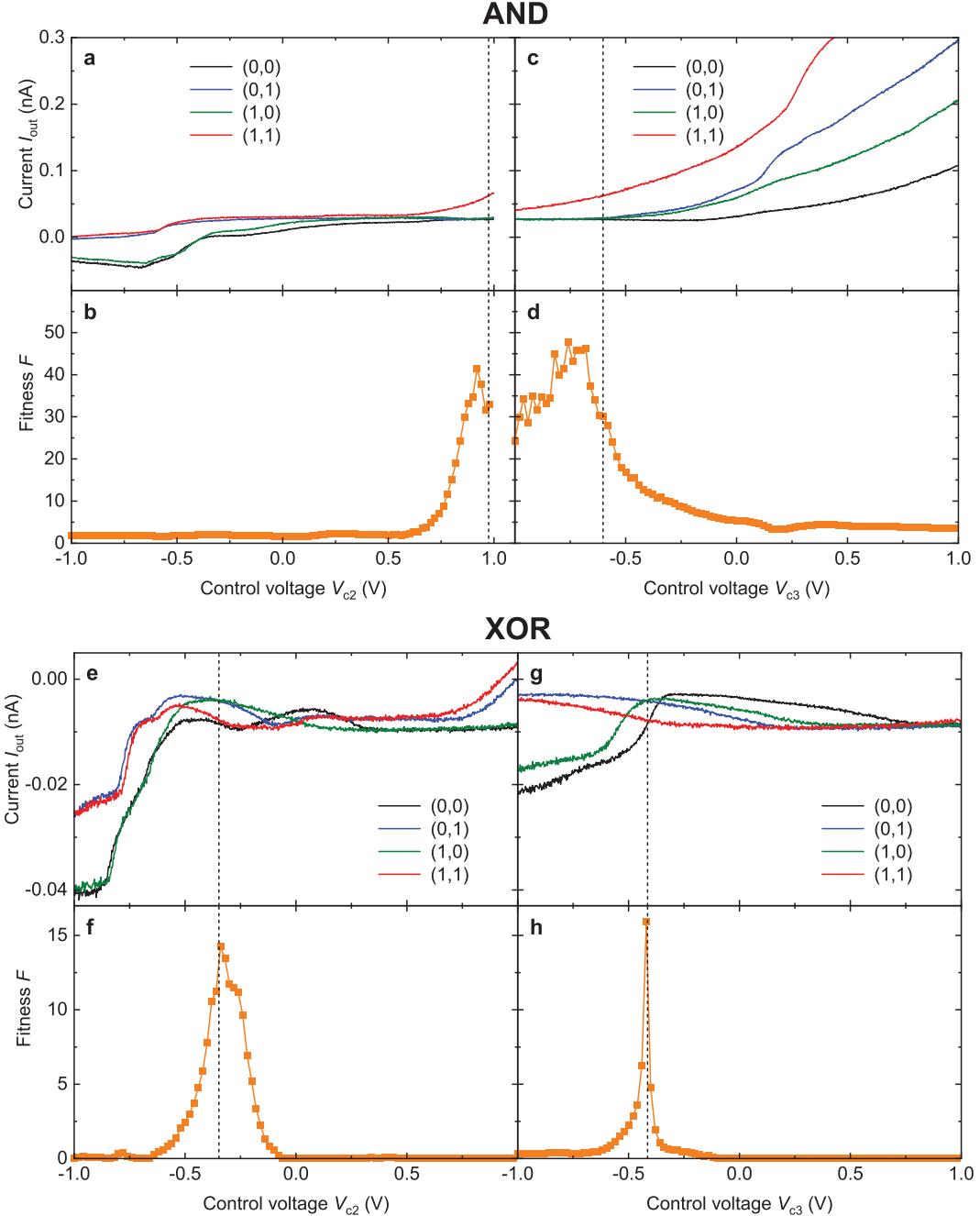

Figure S7. **a**, Output currents  $I_{out}$  for the four logic input combinations and **b** fitness  $F$  of the AND gate of Fig. 2 in the main text as a function of control voltage  $V_{c2}$ . Vertical dashed lines in a and b: value of  $V_{c2}$  found by artificial evolution. **c** and **d**, Same as a and b, but for  $V_{c3}$ . The evolutionary algorithm did not find before stopping the somewhat higher fitnesses of  $F$  in b and d at other values of  $V_{c2}$  and  $V_{c3}$ . **e–h**, Same as a–d, but for the XOR gate.

## S8. GATE ABUNDANCES IN A SECOND DEVICE

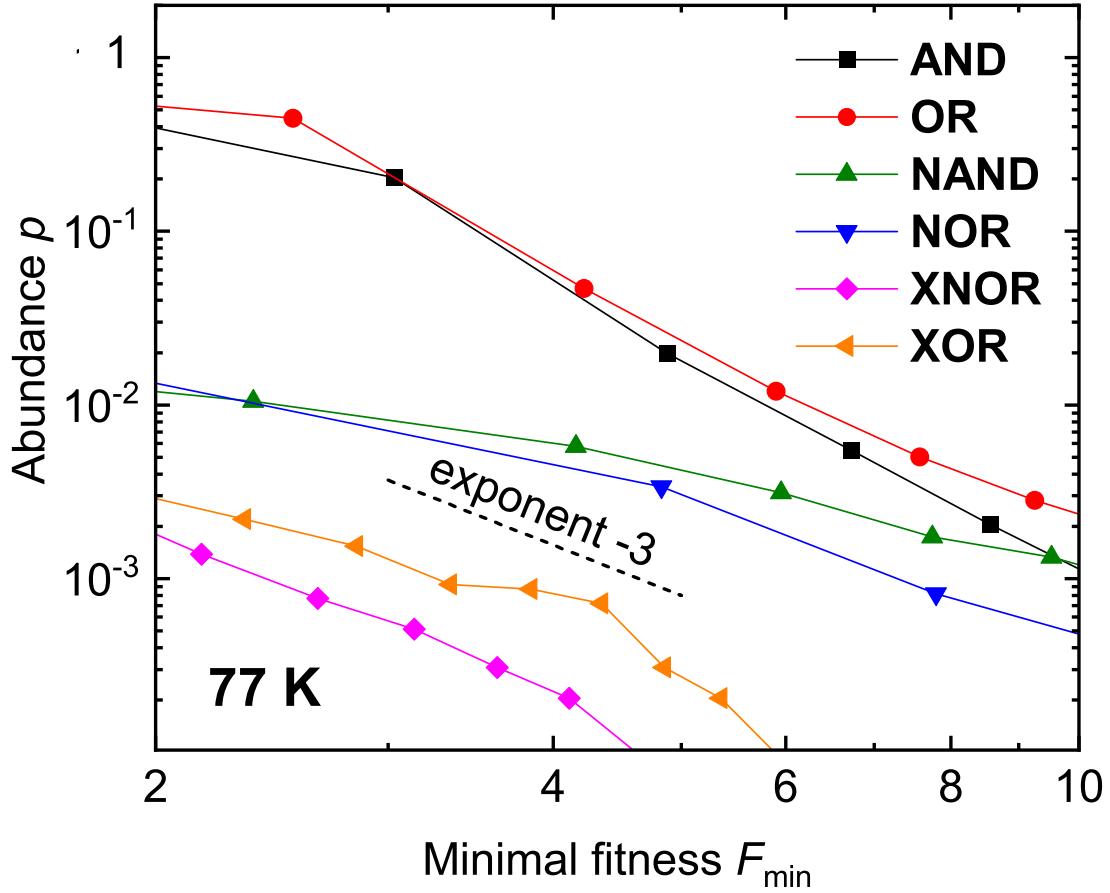

Figure S8. Abundance  $p$  of the six basic Boolean gates with minimal fitness  $F_{\min}$  among about 20,000 random combinations of the control voltages  $V_{c1}$ – $V_{c5}$  of the device in Fig. S2 at 77 K. Fitnesses were obtained from simulations of  $10^7$  KMC steps for each combination. Dashed line: power law with exponent  $-3$ .