# Scalable and Energy-Efficient Peierls Transition Neuron for Monolithic Integrated Neural Network

Seojin Cho<sup>1</sup>, Yuna Kim<sup>1</sup>, Minsu Kang<sup>1</sup>, Hyejin Kim<sup>2</sup>,

Yunsur Kim<sup>3</sup>, Chuljun Lee<sup>4</sup>, Jiyong Woo<sup>3</sup>, Daeseok Lee<sup>1\*</sup>

<sup>1</sup>\*Department of Semiconductor Engineering, Kwangwoon University,

20 Kwangwoon-ro, Seoul, 01897, Nowon-Gu, Republic of Korea.

<sup>2</sup>Department of Electronic Materials Engineering, Kwangwoon

University, 20 Kwangwoon-ro, Seoul, 01897, Nowon-Gu, Republic of

Korea.

<sup>3</sup>School of Electronics Engineering, Kyungpook National University, 80

Daehak-ro, Daegu, 41566, Bukgu, Republic of Korea.

<sup>4</sup>Center for Single Atom-Based Semiconductor Device and Department

of Materials Science and Engineering, Pohang University of Science and

Technology, 77 cheongam-ro, Pohang, 37673, Namgu, Republic of Korea.

\*Corresponding author(s). E-mail(s): [leeds@kw.ac.kr](mailto:leeds@kw.ac.kr);

Contributing authors: [seojin5982@kw.ac.kr](mailto:seojin5982@kw.ac.kr); [xuna37@kw.ac.kr](mailto:xuna37@kw.ac.kr);

[wkdrn5018@kw.ac.kr](mailto:wkdrn5018@kw.ac.kr); [hyejinkim@kw.ac.kr](mailto:hyejinkim@kw.ac.kr); [yunsur.kim@knu.ac.kr](mailto:yunsur.kim@knu.ac.kr);

[leecj@postech.ac.kr](mailto:leecj@postech.ac.kr); [jiyong.woo@knu.ac.kr](mailto:jiyong.woo@knu.ac.kr);

**Keywords:** In-memory computing, Peierls transition,  $\text{NbO}_2$  neuron device, 3D

monolithic integration, ReLU implementation, Neuromorphic hardware

# 1 Note 1: DC Enduracne of $\text{NbO}_2$ based Peierls–Neuron for over 100 switching cycles.

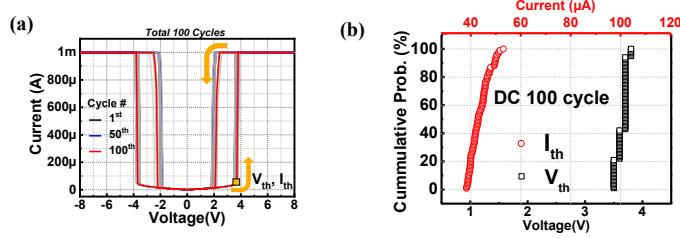

**Fig. 1** (a) DC I-V characteristics of the Peierls-neuron measured over 100 cycles, showing consistent Peierls transitions. (b) Cumulative probability plots of  $V_{th}$  and  $I_{th}$  confirming stable transition behavior.

The cycle-to-cycle Peierls transition uniformity of  $\text{NbO}_2$ -based Peierls-neuron is shown in Supplementary Fig. 1(a). The device was subjected to 100 consecutive DC I-V sweep cycles. Across all cycles, the device consistently exhibited abrupt and repeatable Peierls transition, with a  $V_{th}$  of approximately 3.8 V and an  $I_{th}$  of approximately 40  $\mu\text{A}$ . The cumulative probability distribution further highlighted the reliability of the device. The narrow spread of data, centered at 3.8 V  $V_{th}$  and 40  $\mu\text{A}$   $I_{th}$ , confirmed that the device exhibited excellent uniformity and minimal variation under repeated electrical stress.

These results validated the intrinsic stability of the transition mechanism and confirmed that the Peierls-neuron maintained a reliable performance over repeated operations. Particularly, this performance is advantageous for practical use in hardware-implemented neural networks, where neuron device must endure extensive cycling without performance degradation.

## 2 Note 2: Pulse-driven transitions of the Peierls-neuron.

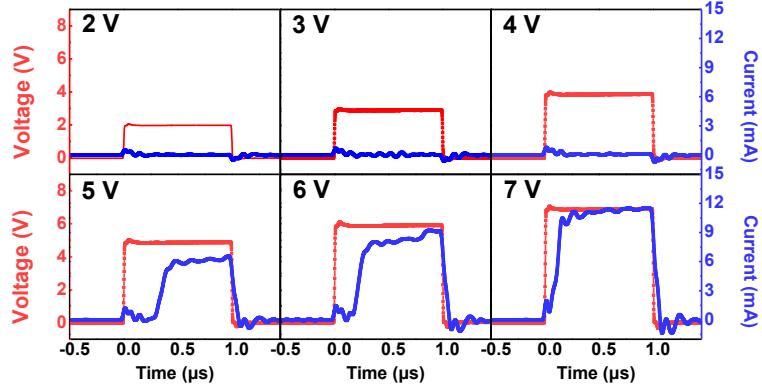

**Fig. 2** Pulse-driven transition dynamics of the Peierls-neuron. Transient voltage and current responses under input pulses ranging from 2 V to 7 V.

Supplementary Fig. 2 presents the experimental validation results of the proposed Peierls-neuron under various input voltage pulses. The experiment was conducted using the circuit setup shown in Fig. 2(d), employing a pulse generator (Agilent 81110A) and a real-time waveform analyzer (CX3300). Time-domain current response under square voltage pulse inputs ranging from 2 V to 7 V were analyzed. At low voltage (2 V), no transition was observed, indicating that the input pulses could not reach the required  $V_{th}$  as identified in the I-V measurement. Conversely, clear current jumps, indicative of a transition into metallic state, were observed at voltage of over 4 V, demonstrating successful ReLU functionality of the Peierls-neuron.

### 3 Note 3: Pulse responses of ReLU operation with various values of $R_P$ .

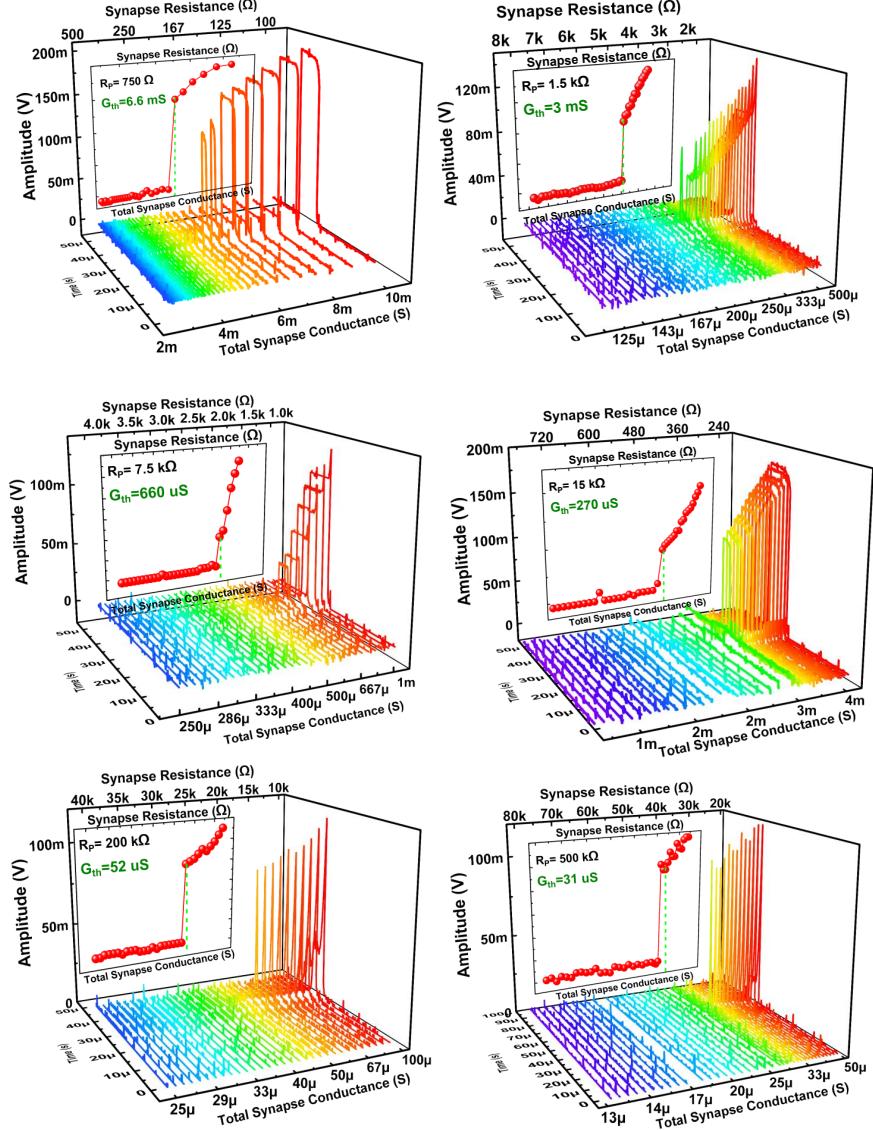

**Fig. 3** Time-domain measurements of the Peierls-neuron under pulse inputs with varying  $R_S$  and  $R_P$  conditions.

Supplementary Fig. 3 illustrates the experimental results. The threshold conductance ( $G_{th}$ ) of the proposed Peierls-neuron was verified to be effectively tuned using a parallel resistor ( $R_P$ ). This finding can be correlated with the results in Fig. 5(a). By adjusting  $R_P$  in parallel with the Peierls-neuron, the summed synaptic current ( $I_S$ ) was partially divided by the branch path parallel to  $R_P$ , allowing flexible control over  $G_{th}$  required for the Peierls-neuron to be compatible with a wide range of synaptic conductance. The total synaptic conductance( $R_S$ ) was calculated by varying the resistance of the synaptic device, and the output voltage ( $V_{out}$ ) was measured using a load resistor of 50  $\Omega$  with an input pulse of 5 V. The measured  $V_{out}$  demonstrated a sharp increase beyond certain conductance values,  $G_{th}$ , confirming that the Peierls-neuron exhibited ReLU functionality.

Pulse responses were obtained for various  $R_P$  values such as 750  $\Omega$ , 1.5 k, 7.5 k, 15 k, 200 k and 500 k. The results confirmed that  $G_{th}$  could be systematically modulated by tuning  $R_P$ . For example, for  $R_P = 7.5$  k,  $G_{th}$  is approximately 660  $\mu$ S, whereas for  $R_P = 15$  k,  $G_{th}$  decreases to approximately 270  $\mu$ S. The results are consistent with those shown in Fig. 5(b). Thus, the value of  $G_{th}$  could be easily tuned depending on the conductance range of the synaptic device providing excellent adaptability to various conductance values of the synaptic device. The inset plots in each sub-figure present the  $G_S$ - $V_{out}$  curves to better visualize  $G_{th}$ .

#### 4 Note 4: Cross-sectional TEM and EDS analyses

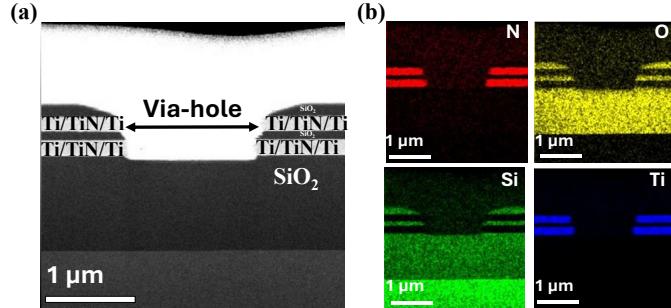

**Fig. 4** (a) Cross-sectional TEM image of the via-hole structure ( $\sim 1.5 \mu\text{m}$  diameter), comprising the Ti/TiN/Ti multilayer electrodes and SiO<sub>2</sub> insulating layers. (b) EDS elemental mapping results for N, O, Si, and Ti, illustrating uniform layer formation and element distribution across the vertical architecture.

Supplementary Fig. 4(a) shows a cross-sectional transmission electron microscopy (TEM) image of a precisely fabricated via-hole structure with a diameter of approximately 1.5  $\mu\text{m}$  embedded within multilayer stacks of Ti/TiN/Ti metal electrodes and SiO<sub>2</sub> were deposited using the radio frequency (RF) and DC sputtering systems. The via-hole was defined using standard photolithography, followed by dry etching to produce the vertical architecture observed in the TEM image. Energy dispersive spectroscopy (EDS) elemental mapping of N, O, Si, and Ti confirmed that each layer was accurately formed in its intended position as shown in supplementary Fig. 4(b). N and Ti were primarily detected in the TiN layer, oxygen was concentrated in the SiO<sub>2</sub> region, and Si was observed on the substrate, indicating well-defined interfacial boundaries. This stable structural platform was reliably maintained throughout the subsequent NbO<sub>X</sub> deposition and high-temperature annealing process and served as a critical foundation for 3D integration of synaptic devices and the Peierls-neuron.

## 5 Note 5: Annealing effect on the Peierls-neuron.

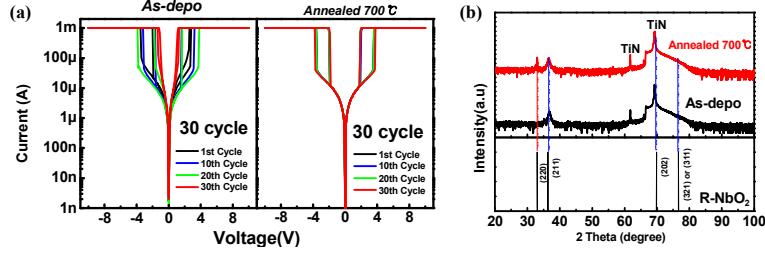

**Fig. 5** (a) Comparison of I-V characteristics, showing significantly improved endurance and stability in the annealed sample. (b) XRD patterns of Peierls-neuron with and without annealing, highlighting the enhanced  $33.02^\circ$  peak indicative of improved tetragonal  $\text{NbO}_2$  crystallinity.

Supplementary Fig. 5 presents a comparative analysis of the electrical switching stability and crystal structure of the  $\text{NbO}_2$ -based Peierls-neuron with and without annealing at  $700^\circ\text{C}$  in a  $\text{N}_2$  atmosphere at ambient temperature. The DC I-V characteristics measured over 30 consecutive cycles demonstrated that  $V_{th}$  fluctuated significantly during cycles in the case without annealing, indicating poor reproducibility of the Peierls transition. Conversely, the device annealed at  $700^\circ\text{C}$  in  $\text{N}_2$  exhibited highly stable  $V_{th}$  positions and consistent current levels throughout all cycles, demonstrating excellent endurance and reliable Peierls transitions. This improvement was attributed to the realignment of grains and the reduction of amorphous phases during annealing, which collectively led to a more uniform electric field distribution across the device [1].

Before annealing, only TiN-related X-ray diffraction (XRD) peaks were observed as shown in supplementary Fig. 5(b). However, after annealing, a strong diffraction peak appeared near  $2\theta = 33.02^\circ$ , corresponding to the (220) plane of tetragonal  $\text{NbO}_2$  (JCPDS No. 01-076-0685). The results confirmed the formation of a crystalline  $\text{NbO}_2$  phase, which was essential for enabling Peierls transition. Thus, the annealing process suppressed the presence of amorphous or  $\text{Nb}_2\text{O}_5$ -dominated region and promotes the selective growth of the  $\text{NbO}_2$  phase, thereby enhancing the overall crystallinity of the active layer [2].

In summary, post-annealing at  $700^\circ\text{C}$  under an  $\text{N}_2$  ambient enabled oxygen redistribution and phase reconstruction, selectively stabilizing the  $\text{NbO}_2$  phase. Consequently, a more uniform electric field distribution and controlled local Joule heating were achieved. This process played a critical role in improving the stability and endurance of the Peierls-neuron.

## References

- [1] Xu, J., Zhu, Y., Liu, Y., Wang, H., Zou, Z., Ma, H., Wu, X., Xiong, R.: Improved performance of nbox resistive switching memory by in-situ n doping. *Nanomaterials* **12**(6), 1029 (2022)

- [2] Nivedita, L., Haubert, A., Battu, A.K., Ramana, C.: Correlation between crystal structure, surface/interface microstructure, and electrical properties of nanocrystalline niobium thin films. *Nanomaterials* **10**(7), 1287 (2020)