# Supplementary Material

## Fabrication and Testing of High-temperature Schottky Diodes

Helei Dong, Liangjie Guo, Chengwei Zhen, Tengteng Dong, He Fu, Xin Tian, Siyu Liang, Rui Feng, Qiulin Tan

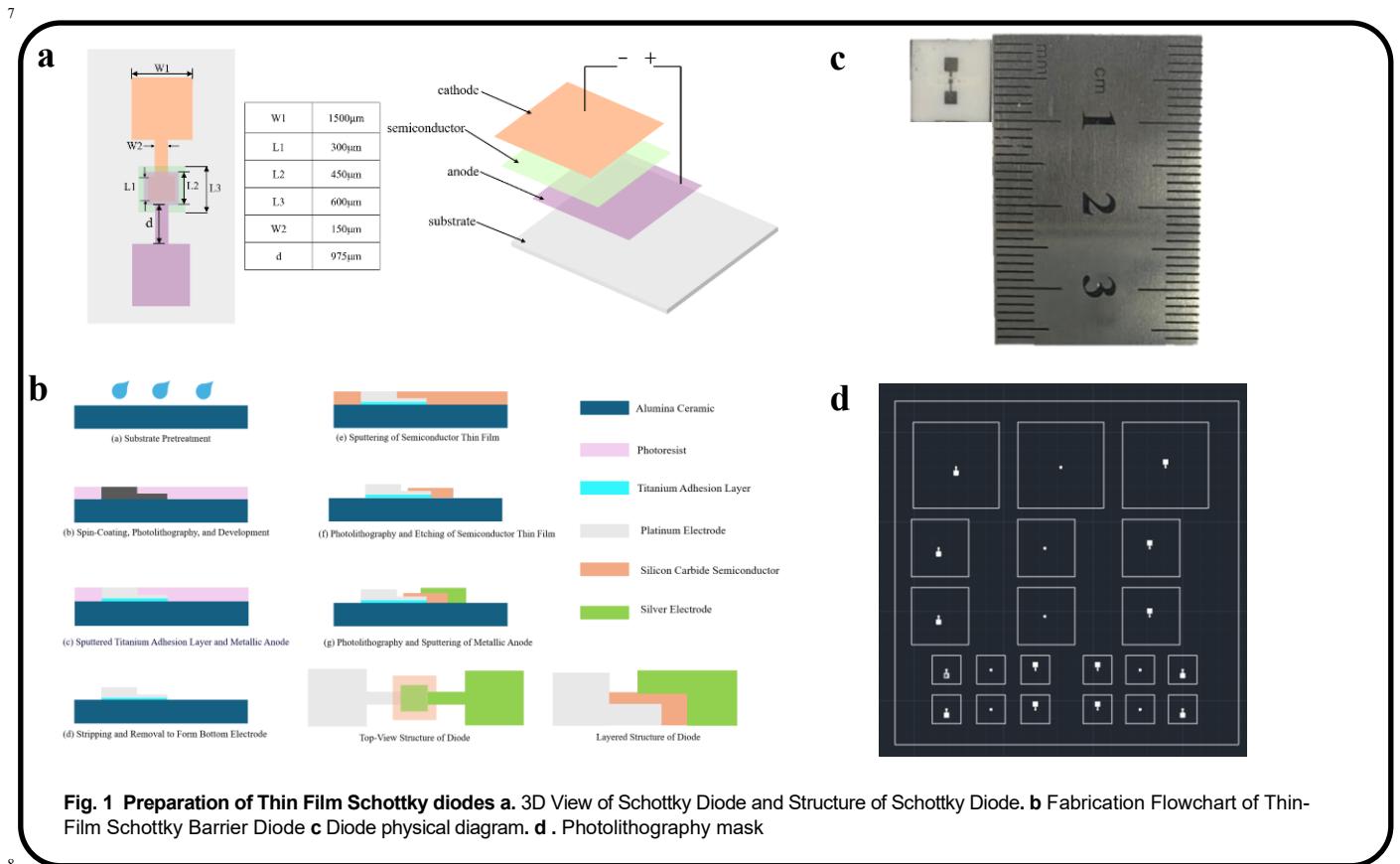

### <sup>1</sup> Fabrication of Thin-Film Schottky Diode

<sup>2</sup> Chottky diode devices are prepared using techniques such as <sup>3</sup> photolithography, electron beam evaporation, and magnetron <sup>4</sup> sputtering. However, since the substrate may contain inorganic <sup>5</sup> contaminants such as dirt or organic contaminants such as bacteria <sup>6</sup> or dander, this can lead to the electrode structure being damaged <sup>7</sup> during subsequent photolithography processing. Therefore, the <sup>8</sup> substrate must be pretreated before preparing the device.

<sup>9</sup> Place the Al<sub>2</sub>O<sub>3</sub> substrate in a clean glass dish and introduce <sup>10</sup> acetone solvent for physical cleaning. Use an ultrasonic cleaner to <sup>11</sup> clean the glass dish for 5 min at high intensity. After ultrasonic <sup>12</sup> cleaning the substrate, place it in an ethanol solution again and <sup>13</sup> perform the same steps as above. After another ultrasonic cleaning, <sup>14</sup> rinse the substrate repeatedly with deionized water until it is pure, <sup>15</sup> and then blow it dry with nitrogen.

### <sup>16</sup> Anode Fabrication

<sup>17</sup> In the process of preparing the anode, the surface of the Al<sub>2</sub>O<sub>3</sub> <sup>18</sup> substrate is first mirror-polished to ensure its flatness, and then a <sup>19</sup> positive photoresist RZJ-304 produced by Suzhou Ruihong is <sup>20</sup> applied by spin coating. This process involves setting specific <sup>21</sup> rotational speed parameters—an initial speed of 500 r/min for 5 s, <sup>22</sup> followed by high-speed spin coating at 3000 r/min for 30 s—to <sup>23</sup> achieve uniform photoresist coating. The spin-coated substrate is <sup>24</sup> preheated at 100 °C for 1 minute to promote the adhesion and <sup>25</sup> curing of the photoresist. The spin-coated substrate is then UV- <sup>26</sup> photolithographed using a mask based on the design shown in <sup>27</sup> Fig.1b. An exposure dose of 80 units is used to ensure accurate <sup>28</sup> pattern transfer. After exposure, the substrate is developed for 20 <sup>29</sup> seconds, rinsed with deionized water (15 seconds per side), and <sup>30</sup> blown dry with nitrogen. It is then post-heated at 120 °C for 1 <sup>31</sup> minute to further cure the pattern.

<sup>32</sup> After that, the bottom electrode of the diode is prepared on the <sup>33</sup> substrate by electron beam evaporation. To enhance the adhesion <sup>34</sup> strength between the bottom electrode and the Al<sub>2</sub>O<sub>3</sub> substrate, a <sup>35</sup> 15 nm thick titanium (Ti) layer is first evaporated on the substrate, <sup>36</sup> taking advantage of its good adhesion to Al<sub>2</sub>O<sub>3</sub>. Then, a 50 nm <sup>37</sup> thick platinum (Pt) layer is evaporated on top as the anode <sup>38</sup> electrode material. After the electrode is prepared, a stripping <sup>39</sup> process is carried out to remove the photoresist from the <sup>40</sup> unilluminated part. This involves dipping the substrate in acetone <sup>41</sup> for 3 minutes, followed by 30 seconds of oscillation using an <sup>42</sup> ultrasonic oscillator, and then an additional 3 minutes of static <sup>43</sup> immersion. Finally, the substrate is rinsed with deionized water <sup>44</sup> and blown dry with a nitrogen gun, and placed on a clean filter

<sup>45</sup> paper for subsequent use. This process ensures the accurate <sup>46</sup> preparation of the anode electrode pattern, laying the foundation <sup>47</sup> for further electronic device manufacturing.

### <sup>48</sup> Fabrication of the semiconductor layer

<sup>49</sup> The substrate should be prepared for the anode by sputtering a <sup>50</sup> SiC semiconductor layer, as outlined in Step 1. It is imperative <sup>51</sup> that this process be conducted under low vacuum conditions at <sup>52</sup> 0.44 Pa. Subsequently, a uniform coating must be applied, the <sup>53</sup> mask template must be aligned according to the design, and a <sup>54</sup> second photolithography must be performed. Subsequent to the <sup>55</sup> development and drying of the photolithographed substrate, it is <sup>56</sup> imperative to adhere to the parameters delineated in Step 1. The <sup>57</sup> culmination of this process entails the etching and peeling of the <sup>58</sup> substrate to achieve the desired semiconductor shape. A series of <sup>59</sup> etching tests were conducted to ascertain the optimal conditions <sup>60</sup> for the etching process. The tests involved the use of concentrated <sup>61</sup> hydrochloric acid (concentration 36%-38%) and deionized water <sup>62</sup> at a ratio of 50:1, with an etching rate of 50 nm and a duration of <sup>63</sup> 100 s.

<sup>64</sup> Following the preparation of the platinum (Pt) electrode, it is <sup>65</sup> essential to promptly deposit the a-IGZO semiconductor layer. <sup>66</sup> The primary composition of the Pt layer deposited by electron <sup>67</sup> beam evaporation is nanoparticles, and Pt is the second most <sup>68</sup> reactive metal after silver (Ag) in air. Prolonged exposure to air <sup>69</sup> may cause oxidation of the Pt layer, which could affect the <sup>70</sup> formation of the Schottky barrier between Pt and SiC and <sup>71</sup> adversely impact device performance.

### <sup>72</sup> Cathode Fabrication

<sup>73</sup> The cathode preparation process commences with the initial <sup>74</sup> step, which encompasses photolithography and development, <sup>75</sup> followed by subsequent thermal treatment. Subsequently, silver <sup>76</sup> (Ag) is deposited as the top cathode electrode on the prepared <sup>77</sup> semiconductor layer using magnetron sputtering technology. The <sup>78</sup> power output is set to 100 watts, with a duration of two minutes, <sup>79</sup> in order to form a 32-nanometer cathode film. Given the stability <sup>80</sup> concerns associated with the semiconductor layer, which is <sup>81</sup> susceptible to chemical reactions and may compromise device <sup>82</sup> performance, it is imperative that cathode deposition be executed <sup>83</sup> expeditiously following the completion of the preparation process. <sup>84</sup> Furthermore, it is imperative to regulate the sputtering thickness <sup>85</sup> of the cathode to below 100 nm. This is to avert the consequences <sup>86</sup> of protracted sputtering, which can result in the infiltration of <sup>87</sup> nano-aluminum particles into the semiconductor layer. Such <sup>88</sup> infiltration can precipitate short circuits and device failure.

<sup>89</sup> The prepared diodes are illustrated in Fig.1c. Throughout the

1 entire preparation process, it is imperative to maintain

2 environmental cleanliness and ensure constant temperature and

3 humidity conditions. These are general requirements in

4 microelectromechanical systems (MEMS) semiconductor

5 processes and are critical for ensuring the successful preparation

6 and stable performance of the devices

**Fig. 1 Preparation of Thin Film Schottky diodes** **a.** 3D View of Schottky Diode and Structure of Schottky Diode. **b.** Fabrication Flowchart of Thin-Film Schottky Barrier Diode **c** Diode physical diagram. **d** . Photolithography mask

8

9

## 10 Experimental results and discussion

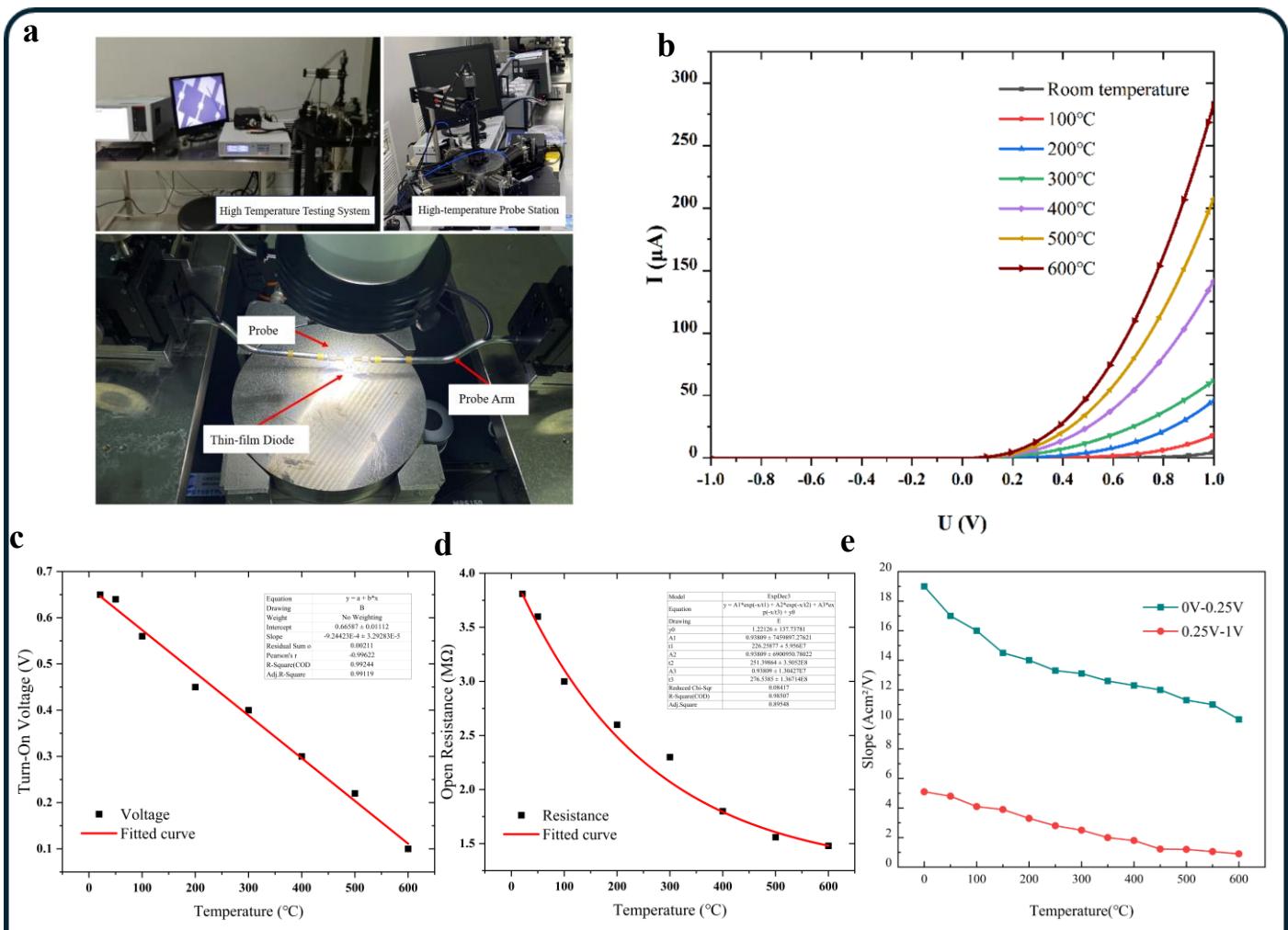

11 In order to verify the performance and nonlinear characteristics

12 of the Schottky diode at high temperatures, the diode is tested at

13 temperature using a device temperature test system consisting of

14 a Keithley 4200A-SCS parameter analyzer, a Lakeshore Model

15 CRX-6.5K high and low temperature probe station, a Lakeshore

16 336 temperature controller, a pump and a refrigeration cycle. As

17 shown in Fig.2a, When the probe contacts the object to be tested,

18 the temperature sensor on the probe can accurately measure the

19 temperature, enabling real-time measurement. The internal

20 temperature measurement error does not exceed 0.5°C within a

21 range of room temperature to 600°C.

22 In a high-temperature test environment, the oxidation protection

23 of metal components and test probes is particularly critical.

24 Therefore, vacuum refrigeration technology is introduced to

25 ensure that the sample chamber is always maintained in a high

26 vacuum during the test. The conversion of the mechanical pump

27 to a molecular pump can improve the vacuum rate, and then the

28 test chamber is subjected to a cold cycle treatment, which can

29 ensure the temperature balance of the test system during testing at

30 different temperatures, and ensure that the system is not damaged

31 due to excessive temperature differences.

32 The data from the parameter analyzer Keithley 4200A-SCS

33 was recorded every 50 °C based on a set temperature step of

34 21 °C. The recorded data is plotted in Fig.2b, which shows a set

35 of I-V characteristic curves of the diode in the temperature range

36 of 21-600 °C.

37 As can be seen from Fig.2b, the current-voltage curve exhibits

38 a nonlinear characteristic, and as the temperature increases, the

39 curve gradually shifts from right to left. Plot the measured voltage

40 versus temperature curve, as shown in Fig.2c. When the

41 temperature rises to 600 degrees Celsius, the Schottky diode

42 voltage gradually decreases with increasing temperature,

43 gradually decreasing from 0.65V to 0.1V. and the voltage

44 attenuation rate is calculated to be 0.92mV/°C. The resistance

45 change curve obtained by plotting and calculating is shown in

46 Fig.2d. The resistance decreases from 3.61kΩ to 1.53kΩ, and the

47 average resistance attenuation rate is calculated to be 3.43Ω/°C.

48 According to the slope of the current change, the voltage has a

49 smaller slope at 0-0.25 V and a larger slope at 0.25-1. In order to

50 facilitate data comparison, the measured current-voltage curve

51 from room temperature to 600°C is converted into a junction

52 current-voltage (J-V) characteristic curve. According to the

53 formula for junction current density<sup>1</sup>:

$$54 \quad J = A * T^2 \exp\left(\frac{-q\phi_{BO}}{kT}\right) \left[ \exp\left(\frac{qV}{nkT}\right) - 1 \right] \quad (1)$$

55 When the forward voltage is low (approximately 0–0.25 V), as

56 the temperature increases, the slope of the I-V curve in the low-

57 voltage range gradually decreases. The term  $q/nkT$  in Equation 1

58 represents the slope of the curve, and as T increases, this term

59 decreases. By performing segmented linear fitting on the curves

1 in Fig 2b, the temperature-dependent slope curves of the two sets

2 of curves are fitted within the forward voltage ranges of 0–0.25 V

3 and 0.74–1 V. The temperature-dependent slope curves of the 21–

4 600°C range are shown in Fig 2e.

5 The slope of the I-V curve in the forward voltage range of 0–

6 0.25V is significantly higher than that in the range of 0.74–1V. As

7 the forward voltage increases, the I-V curve of the diode tends to

8 the ideal diode characteristic when the voltage is in the 0.74–1V

9 range, and the fit of the curve improves accordingly with

10 increasing temperature. This is because the equivalent resistance

11 of the diode decreases at high temperatures, thereby reducing the

12 impact of resistance on the performance of the entire device.

13 Although increasing temperature causes the resistivity of the

14 metal cathode and anode to increase, the resistance of the

15 semiconductor layer tends to decrease. In this experiment, the

16 diode's equivalent resistance decreases, which indicates that the

33

17 effect of temperature on the resistivity of the semiconductor layer

18 is more significant than its effect on the metal electrodes. When

19 the forward voltage exceeds the diode's turn-on voltage, the slope

20 of the curve decreases significantly compared to the first half, and

21 the slope can be regarded as the reciprocal of the equivalent

22 resistance, which means that the diode's equivalent resistance

23 increases in the second half, and the resistance plays a major role

24 in reducing the current at this time.

25 Verification shows that as the temperature of the diode increases,

26 the I-V characteristic curve becomes nonlinear and shifts to the

27 right. The diode's ideality factor gradually decreases with

28 increasing temperature, while the barrier height gradually

29 increases with increasing temperature. This characteristic meets

30 the performance requirements for operation at high temperatures,

31 confirming the correctness of the diode operating at high

32 temperatures.

**Fig. 2 Test and Analysis** **a.** Thin-film diode high-temperature characteristic test system. **b** Schottky Diode I-V Characteristic Curves **c** Schottky diode turn-on voltage. **d** Schottky diode turn-on resistance. **e** Diode current density at different voltages.